# CHAPTER 9

## **Protecting Diodes, Transistors,** and Thyristors

All power switching devices attain better switching performance if some form of switching aid circuit, called snubber, is employed. Snubber activation may be either passive or active which involves extra power switches. Only passive snubbers, which are based on passive electrical components, are considered in this chapter, while active snubbers are considered in Chapter 10. Fundamentally, the MOSFET and IGBT do not require switching aid circuits, but circuit imperfections, such as stray inductance and diode recovery, can necessitate the need for some form of switch snubber protection. Protection in the form of switching aid circuits performs three main functions:

- Divert switching losses from the switch thereby allowing a lower operating temperature, or higher electrical operating conditions for a given junction temperature.

- Prevent transient electrical stressing that may exceed *I*-*V* ratings thereby causing device failure.

- Reduce conducted and radiated electromagnetic interference

Every semiconductor switching device can benefit from switching protection circuits, but extra circuit component costs and physical constraints may dictate otherwise.

The bipolar diode suffers from reverse recovery current and voltage snap which induces high but short duration circuit voltages. These voltage transients may cause interference to the associated circuit and to nearby equipment. A simple series non-polarised *R*-*C* circuit connected in parallel to the stressed or offending device is often used to help suppress the voltage oscillation at diode turn-off. Such a suppression circuit can be effectively used on simple mains rectifying circuits when rectification causes conducted and radiated interference.

Although the MOSFET and IGBT can usually be reliably and safely operated without external protection circuitry, stringent EMC application emission restrictions may dictate the use of snubbers. In specific applications, the IGBT is extensively current derated as its operating frequency increases. In order to attain better device current utilization, at higher frequencies, various forms of switching aid circuits can be used to divert switching losses from the stressed semiconductor switch.

Generally, all thyristor devices benefit from a polarised turn-on switching aid circuit, which is based on a series connected inductor that is active at thyristor turn-on. Such an inductive turn-on snubber is obligatory for the high-power GCT and GTO thyristor. In order to fully utilise the GTO thyristor, it is usually used in conjunction with a parallel-connected capacitive turn-off snubber, which decreases device stressing during the turn-off transient. Triacs and rectifier grade SCRs and diodes tend to use a simple R-C snubber connected in parallel to the switch to reduce interference. The design procedure of the R-C snubber for a diode is different to that for the R-C snubber design for a thyristor device, because the protection objectives and initial conditions are different. In the case of a thyristor or rectifier diode, the objective is to control both the voltage rise at turn-off and recovery overshoot effects. For the fast recovery diode or any high-speed switch, the principal objectives are to control the voltage overshoot magnitude at diode snap recovery or at turn-off respectively, which are both exacerbated because of stray circuit inductance carrying current.

#### 9.1 The non-polarised *R*-*C* snubber

The series *R*-*C* snubber is the simplest switching aid circuit and is connected in parallel to the device being aided. It is characterized by having low series inductance and a high transient current rating. These requirements necessitate carbon type resistors for low inductance, below a few watts, and metal film resistors at higher powers. The high current and low inductance requirements are also provided by using metallised, polypropylene capacitors with high dv/dt ratings of typically hundreds of V/µs.

Theoretically a purely capacitive snubber would achieve the required protection objectives, but series resistance is added to decrease the current magnitude when the capacitor is discharging and to damp any voltage oscillation by dissipating the oscillatory energy generated at turn-off when an over-voltage tends to occur.

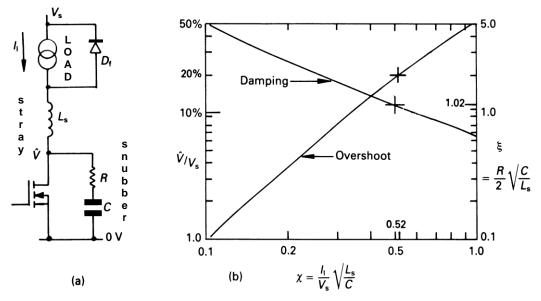

Figure 9.1. MOSFET drain to source R-C snubber protection: (a) MOSFET circuit showing stray inductance, L<sub>s</sub>, and R-C protection circuit and (b) R-C snubber optimal design curves.

#### 9.1.1 R-C switching aid circuit for the GCT, the MOSFET, and the diode

In figure 9.1a, at switch turn-off, stray inductance  $L_s$  unclamped by the load freewheel diode,  $D_h$ , produces an over voltage  $\hat{V}$  on the MOSFET or IGBT. The energy associated with the inductor can be absorbed in the shown drain to source connected *R*-*C* circuit, thereby containing the voltage overshoot to a controlled safe level. Such an *R*-*C* snubber circuit is used extensively in thyristor circuits, 9.1.2, for dv/dt protection, but in such cases the initial current in the stray inductance is assumed zero. Here the initial inductor current is equal to the maximum load current magnitude,  $I_\ell$ . The design curves in figure 9.1b allow selection of *R* and *C* values based on the maximum voltage overshoot  $\hat{V}$  and an initial current factor  $\chi$ , defined in figure 9.1b. The *C* and *R* values are given by

$$C = L_s (I_\ell / \chi V_s)^2$$

(F) (9.1)

$$R = 2\xi V_s \chi / I_\ell \qquad (\Omega) \qquad (9.2)$$

If the *R*-*C* circuit time constant,  $\tau = RC$ , is significantly less than the MOSFET voltage rise and fall times,  $t_{rv}$  and  $t_{fv}$ , at reset (when the capacitor is discharged through the resistor and switch at turned on), a portion of the capacitor energy  $\frac{1}{2}CV_s^2$ , is dissipated in the switch, as well as in *R*. The switch appears as a variable resistor in series with the *R*-*C* snubber. Under these conditions ( $t_{fv}$  and  $t_{rv} > RC$ ) the resistor power loss is approximately by

$$P_{R} = P_{Ron} + P_{Roff}$$

$$= \frac{\tau}{\tau + t_{fv}} P_{C0} + \frac{\tau}{\tau + t_{rv}} (P_{C0} + P_{L0}) \qquad (W) \qquad (9.3)$$

where  $P_{C0} = \frac{1}{2}CV_s^2 f_s$  and  $P_{L0} = \frac{1}{2}L_s I_\ell^2 f_s$

otherwise ( $t_{fv}$  and  $t_{rv} < RC$ ) the resistor losses are the energy to charge and discharge the snubber capacitor, plus the energy stored in the stray inductance, that is  $2P_{C0} + P_{L0}$ .

Note the total losses are independent of snubber resistance. The snubber resistor determines the time over which the energy is dissipated, not the amount of energy dissipated.

When the *R*-*C* snubber is employed across a fast recovery diode, the peak reverse recovery current is used for  $I_{\ell}$  in the design procedure.

### Example 9.1: R-C snubber design for MOSFETs

A MOSFET switches a 40 A inductive load on a 200 V dc rail, at 10 kHz. The unclamped drain circuit inductance is 20 nH and the MOSFET voltage rise and fall times are both 100 ns. Design a suitable *R*-*C* snubber if the MOSFET voltage overshoot is to be restricted to 240 V (that is, 40V overshoot, viz. 20%).

#### Solution

From figure 9.1b, for 20 per cent voltage overshoot

$$\xi = 1.02, \ \chi = 0.52$$

Using equations (9.1) and (9.2) for evaluating C and R respectively,

$$C = L_{s} (I_{\ell} / \chi V_{s})^{2} = 20 \text{nH} \left(\frac{40\text{A}}{0.52 \times 200\text{V}}\right)^{2} = 3\text{nF}$$

$$R = 2\xi V_{s} \chi / I_{\ell} = 2 \times 1.02 \times \frac{0.52 \times 200\text{V}}{40\text{A}} = 5.3\Omega$$

Use C=3.3 nF, 450V dc, metallised polypropylene capacitor and R=5.6  $\Omega$ .

Since the *RC* time constant, 18.5ns, is short compared with the MOSFET voltage transient times, 100ns, the resistor power rating is given by equation (9.3).

$$P_{C0} = \frac{1}{2}CV_s^2 f_s = \frac{1}{2} \times 3.3 \text{nF} \times 200^2 \times 10 \text{kHz} = 2.64\text{W}$$

$$P_{L0} = \frac{1}{2}L_s I_\ell^2 f_s = \frac{1}{2} \times 20 \text{nH} \times 40^2 \times 10 \text{kHz} = 0.16\text{W}$$

$$P_R = \frac{18.5 \text{ns}}{100 \text{ns} + 18.5 \text{ns}} \times 2.64\text{W} + \frac{18.5 \text{ns}}{100 \text{ns} + 18.5 \text{ns}} \times (2.64\text{W} + 0.16\text{W}) = 0.85\text{W}$$

Use a 5.6  $\Omega$ , 1 W carbon composition resistor for low self-inductance, with a working voltage of at least 250V dc. Parallel connection of two 12 $\Omega$  ½W, carbon composition resistors may be necessary since resistance values below 10 $\Omega$  are uncommon.

The MOSFET switching losses are  $2W_{C0} + P_{L0} - 0.85W = 4.95W$  higher than those incurred by switching un-aided at 200V and 40A. From equations 7.9 and 7.10, the switching losses would be at least 8W, (4W+4W).

#### 4

#### 9.1.2 Non-polarised R-C snubber circuit for a converter grade thyristor and a triac

The snubber circuit for a low switching frequency thyristor is an anode-to-cathode parallel connected R-C series circuit for off-state voltage transient suppression. Thyristor series inductance may be necessary (forming a turn-on snubber) to control anode di/dt at turn-on. This inductive snubber is essential for the GCT and the GTO thyristor, and will be considered in section 9.3.3.

#### Off-state dv/dt suppression snubber

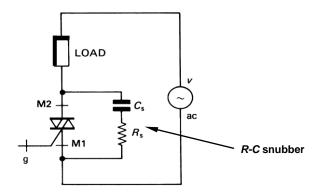

Thyristors, other than the GCT and the GTO thyristor, normally employ a simple *R*-*C* snubber circuit as shown in figure 9.2. The purpose of the *R*-*C* snubber circuit is not primarily to reduce turn-off switching loss but rather to prevent false triggering (turn on) from applied or reapplied anode dv/dt, when the switch is in a forward voltage blocking off-state.

Any thyristor rate of rise of forward-voltage anode dv/dt produces a central junction charging current which may cause the thyristor to inadvertently turn on. The critical dv/dt is defined as the minimum value of dv/dt which will cause switching from the off-state to the on-state. In applications as shown in figure 9.2, an occasional false turn-on is generally not harmful to the triac or the load, since the device and the load only have to survive the surge associated with a half-a-cycle of the ac mains voltage supply.

In other applications, such as reversible converters, a false dv/dt turn-on may prove catastrophic. A correctly designed snubber circuit is therefore essential to control the rate of rise of anode voltage.

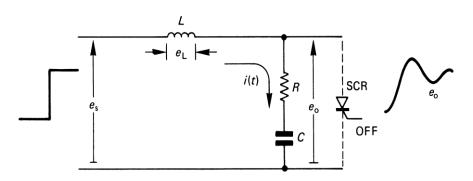

The action of this *R*-*C* snubber circuit relies on the presence of inductance in the main current path. The inductance may be stray, from transformer leakage or a supply, or deliberately introduced. Zero inductor current is the initial condition, since the device is in the off-state when experiencing the anode positive dv/dt. Analysis is based on the response of the *R*-*C* portion of an *L*-*C*-*R* circuit with a step input voltage and zero initial inductor current. Figure 9.3 shows an *L*-*C*-*R* circuit with a step input voltage and the typical resultant voltage across the SCR or *R*-*C* components. The circuit resistor *R* damps (by dissipating power) any oscillation and limits the capacitor discharge current through the SCR at subsequent SCR device turn-on initiated from the gate. The snubber resistor dissipates power even if the triac is not switching, since the snubber capacitor voltage alternates, tracking the ac voltage supply.

Figure 9.2. Thyristor (triac) ac circuit with an R-C snubber circuit.

Figure 9.3. Non-polarised R-C snubber equivalent circuit showing the second-order output response  $e_0$  to a step input voltage  $e_s$ .

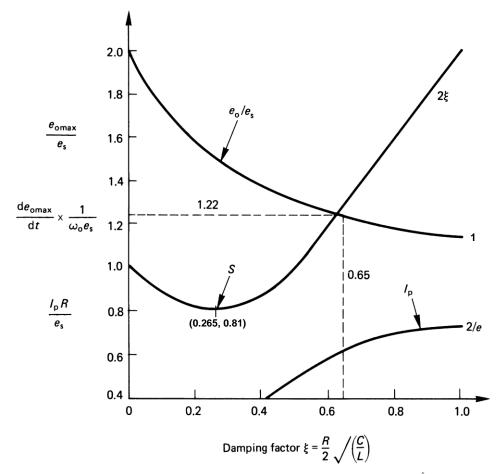

Figure 9.4. Variation of snubber peak voltage,  $e_o$ , maximum  $de_o/dt$ ,  $\hat{S}$ ; and peak current,  $I_p$ ; with L-C-R damping factor  $\xi$ .

Based on the snubber circuit analysis presented in the appendix in section 9.5 at the end of this chapter, the maximum dv/dt,  $\hat{S}$ , which is usually specified for a given device, seen by the SCR for a step input of magnitude  $e_s$ , is given by

$$\hat{S} = e_s R / L \qquad (V/s) \tag{9.4}$$

for a damping factor of  $\xi > \frac{1}{2}$ . That is, after rearranging, the snubber resistance is given by

$$R = L\hat{S}/e_s \qquad \text{(ohms)} \tag{9.5}$$

while the snubber capacitance is given by

$$=\frac{4\xi^2 e_s}{R\hat{S}}$$

(F) (9.6)

and the peak snubber current is approximated by

С

$$\hat{I} = \frac{e_s}{R} \frac{2\xi}{\sqrt{1-\xi^2}}$$

(A) for  $\xi < 1$ . (9.7)

Figure 9.4 shows the variation of the different normalised design factors, with damping factor  $\xi$ .

#### **Example 9.2:** Non-polarised R-C snubber design for a converter grade thyristor

Design an *R*-*C* snubber for the SCRs in a circuit where the SCRs experience an induced *dv/dt* due to a complementary SCR turning on, given

- peak switching voltage, e<sub>s</sub> = 200 V

- operating frequency, f<sub>s</sub> = 1 kHz

- *dv/dt* limit, *S* = 200 V/μs.

Assume

- stray circuit  $L = 10 \,\mu\text{H}$

- 22 per cent voltage overshoot across the SCR

- an *L-C-R* snubber is appropriate.

#### Solution

From equation (9.5) the snubber resistance is given by

$$R = L\hat{S}/e_s$$

$$= \frac{10\mu H \times 200V/\mu s}{200V} = 10\Omega$$

At turn-on the additional anode current from the snubber capacitor will be  $200V/10\Omega = 20A$ , which decays exponentially to zero, with a  $1.8\mu s$  ( $10\Omega \times 180nF$ ) *RC* time constant.

Figure 9.4 shows the *R*-*C* snubber circuit overshoot voltage magnitude,  $\hat{e}_0/e_s$  for a range of damping factors  $\xi$ . The normal range of damping factors is between  $\frac{1}{2}$  and 1. Thus from figure 9.4, allowing 22 per cent overshoot, implies  $\xi = 0.65$ . From equation (9.6)

$$C = \frac{4\xi^2 e_s}{R \,\hat{S}} = \frac{4 \times (0.65)^2 \times 200V}{10\Omega \times 200 \times 10^6}$$

= 180 nF (preferred value) rated at >244 V peak.

From equation (9.7) the peak snubber current during the applied dv/dt is

$$\hat{I} = \frac{e_s}{R} \frac{2\xi}{\sqrt{1 - \xi^2}} = \frac{200V}{10\Omega} \frac{2 \times 0.65}{\sqrt{1 - 0.65^2}} = 34 \text{ A}$$

The 10 ohm snubber resistor losses are given by

$$P_{10\Omega} = C e_0^2 f_s$$

= 180×10<sup>.9</sup>×244<sup>2</sup>×1×10<sup>3</sup> = 11W

Resistor current flows to both charge (maximum 34A) and discharge (initially 20A) the capacitor.

The necessary 10 $\Omega$ , 11W resistor must have low inductance, hence two 22  $\Omega$ , 7W, 500V dc working voltage, metal oxide film resistors can be parallel connected to achieve the necessary ratings.

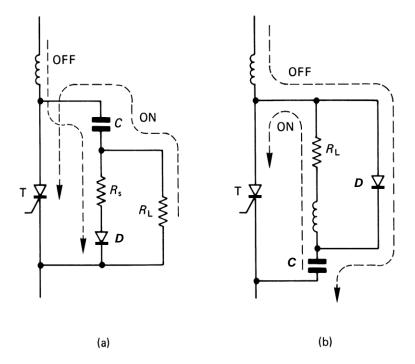

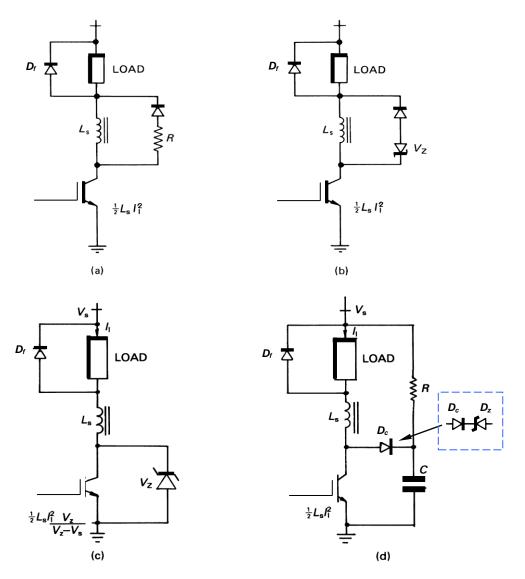

Variations of the basic *R*-*C* snubber circuit are shown in figure 9.5. These circuits use extra components in an attempt to control SCR initial *di/dt* arising from snubber discharge through  $R_L$  at thyristor turn-on. Figure 9.5a has the disadvantage that three series devices (*C*-*R*<sub>s</sub>-*D*) provide turn-off protection. The parasitic series inductance can be decreased by using a turn-off snubber with two series components (*C*-*D*), as shown in figure 9.5b.

An *R*-*C* snubber can be used across a diode in order to control voltage overshoot at diode snap-off during reverse recovery, as a result of stray circuit inductance, as considered in 9.1.1.

The *R*-*C* snubber can provide decoupling and transient overvoltage protection on both ac and dc supply rails, although other forms of *R*-*C* snubber circuit may be more applicable, specifically the soft voltage clamp.

Figure 9.5. Polarised variations of the basic thyristor R-C snubber: (a)  $R_s << R_L$  and (b) transistor-type R-C-D snubber,  $R_s = 0$ .

#### 9.2 The soft voltage clamp

A primary function of the basic *R*-*C* snubber is to suppress voltage overshoot levels. The *R*-*C* snubber commences its clamping action from zero volts even though the objective is to clamp any switch overvoltage to the supply voltage level,  $V_s$ . Any clamping action below  $V_s$  involves an unnecessary transfer of energy. The soft voltage clamp reduces energy involvement since it commences clamping action once the switch voltage has reached the supply voltage  $V_s$ , and the voltage overshoot commences.

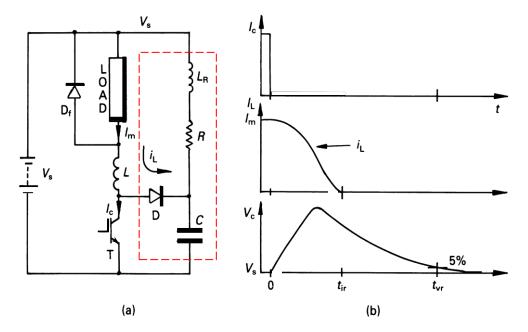

The basic polarised *R*-*C*-*D* soft voltage clamp is shown in figure 9.6a, with resistor *R* parasitic inductance,  $L_R$ , and stray or deliberately introduced unclamped inductance *L*, shown.

The voltage clamp functions at switch turn-off once the switch voltage exceeds  $V_s$ . The capacitor voltage never falls below the supply rail voltage  $V_s$ . Due to the stored energy in L, the capacitor C charges above the rail voltage and R limits current magnitudes as the excess capacitor charge discharges through R in to  $V_s$ . All the energy stored in L,  $\frac{1}{2}LI_m^2$ , is dissipated in R. The inductor current  $i_L$  and capacitor voltage  $V_c$  waveforms are shown in figure 9.6b.

At switch turn-on, the diode D blocks, preventing discharge of C which remains charged to V<sub>s</sub>.

The energy drawn from the supply  $V_s$  as the capacitor overcharges, is returned to the supply as the capacitor discharges through R into the supply. The net effect is that only the energy in L,  $\frac{1}{2}LI_m^2$ , is dissipated in R.

Analysis is simplified if the resistor inductance  $L_R$  is assumed zero. The inductor current decreases from  $I_m$  to 0 according to

where

$$i_{L}(\omega t) = I_{m} {}^{\omega_{0}} / \omega e^{-\alpha t} \cos(\omega t - \phi) \qquad (A) \qquad (9.8)$$

$$\frac{\alpha}{\omega} = \sqrt{2RC} \qquad (s) \qquad \omega_{o} = 1 / \sqrt{LC} \qquad (rad/s)$$

$$\omega = \sqrt{\omega_{o}^{2} - \alpha^{2}} \qquad (rad/s) \qquad \phi = \tan^{-1} \alpha / \omega \qquad (rad)$$

Figure 9.6. Soft voltage polarised clamp: (a) circuit diagram and (b) turn-on inductor current,  $I_L$ , and capacitor voltage,  $V_c$ , at switch turn-off.

The inductor current reaches zero, termed the current reset time,  $t_{ir}$ , in time

$$t_{ir} = (\frac{1}{2}\pi + \phi)/\omega$$

(S) (9.9)

must be shorter than the switch minimum off-time,  $\check{t}_{off}$ . The capacitor charges from  $V_s$  according

which r to

$$V_{c}(\omega t) = V_{s} + \frac{I_{m}}{\omega C} e^{-\alpha t} \sin \omega t \quad (V)$$

(9.10)

The maximum capacitor voltage, hence maximum switch voltage, occurs for large R

$$\hat{V}_{c} = V_{s} + I_{m} \sqrt{\frac{L}{C}}$$

(V) (9.11)

Once the current in L has reduced to zero the capacitor discharges to  $V_s$  exponentially, with a time constant RC.

The practical *R*-*C* circuit, which includes the stray inductance  $L_R$ , must be over-damped, that is

$$R > 2\sqrt{\frac{L_R}{C}} \qquad (\Omega) \tag{9.12}$$

The capacitor voltage reset time  $t_{vr}$  is the time for the capacitor to discharge to within 5 per cent of  $V_{s}$ , as shown in figure 9.6b.

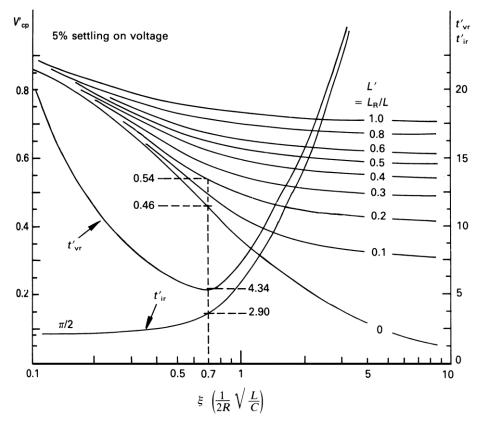

The stray inductance  $L_R$  increases the peak capacitor voltage and increases the voltage reset time. Design of the voltage clamp, including the effects of  $L_{R_2}$  is possible with the aid of figure 9.7. Design is based on specifying the maximum voltage overshoot,  $V_{cp}$  and minimizing the voltage reset time,  $t_{vr}$ , which limits the upper switching frequency,  $f_s$ , where  $f_s \leq 1/t_{vr}$  such that  $\check{t}_{off} \geq t_{ir}$ .

#### Example 9.3: Soft voltage clamp design

A 5 µH inductor turn-on snubber is used to control diode reverse recovery current and switch turn-on loss, as shown in figure 9.6a. The maximum collector current is 25 A, while the switch minimum off-time is 5 µs and the maximum operating frequency is 50 kHz.

- i. Assuming an independent L-C resonant transfer from L to C and a subsequent R-C discharge cycle, calculate soft voltage clamp R and C requirements.

- ii. Use figure 9.7 to determine the voltage clamp requirements if the discharge (reset) resistor inductance  $L_R$  is

- (a)

- 0 (b) 1.0µH.

In each case, the maximum switch overshoot is to be restricted to 50 V.

Figure 9.7. Voltage clamp capacitor normalised peak over-voltage,  $V_{Cp}$ , versus damping factor,  $\xi$ , for different resistor normalised inductances, L', and voltage and current normalised settling times,  $t'_{vr}$ ,  $t'_{ir} = V_{cp} / \{I_m \sqrt{L/C}\}$ ,  $t'_{vr} = t_{rv} / \omega_0$ ,  $t'_{ir} = t_{ir} / \omega_0$ .

#### Solution

*i.* Assuming all the inductor energy is transferred to the clamp capacitor, before any discharge through *R* occurs, then from equation (9.11), for a 50 V capacitor voltage rise

$$50 = I_m \sqrt{\frac{L}{C}}$$

that is,  $C = 5 \mu H/(50V/25A)^2 = 1.25 \mu F$  (use 1.2  $\mu$ F, rated at, at least 50V above the dc supply  $V_s$ ).

From equation (9.9), for R = 0, the energy transfer time (from L to C) is

$$t_{jr} = \frac{1}{2}\pi \sqrt{LC} = \frac{1}{2}\pi \sqrt{5\mu H \times 1.25\mu F} = 4\mu s$$

which, as required, is less than the switch minimum off-time of 5 µs.

If the maximum operating frequency is 50 kHz, the capacitor must discharge in 20 - 4 = 16  $\mu$ s.

Assuming five RC time constants for capacitor discharge

$$5 \times RC = 16 \mu s$$

$$R = 16\mu s/(5 \times 1.2\mu F) = 2\frac{3}{3}\Omega$$

(use 2.4 $\Omega$ )

The resistor power rating is

$$P_{R} = \frac{1}{2}LI_{m}^{2}f_{s} = \frac{1}{2}\times5\mu H\times25^{2}\times50kHz = 78W$$

Obviously with a 2.4  $\Omega$  discharge resistor and 50V overshoot, discharge current would flow as the capacitor charges above the voltage rail. A smaller value of *C* could be used. A more accurate estimate of *C* and *R* values is possible, as follows.

*ii.* (a)

$$L_R = 0$$

, that is  $L' = L_R/L = 0$

From figure 9.7, for the minimum voltage reset time, as indicated

$V_{cp}^{i} = 0.46$ ,  $t_{ir}^{i} = 2.90$ ,  $t_{rv}^{i} = 4.34$ , and  $\xi = 0.70$

From  $V_{cp}^{i} = V_{cp} / I_m \sqrt{L_C'}$

$0.46 = 50V/25A \sqrt{5\mu H_C}$  gives  $C = 0.27\mu F$

From  $\xi = \frac{1}{2R}\sqrt{\frac{L}{C}}$ ,  $R = \frac{1}{2\xi}\sqrt{\frac{L}{C}} = \frac{1}{2 \times 0.7}\sqrt{\frac{5\mu H}{0.27\mu F}} = 3.2\Omega$ (Use 3.3  $\Omega$ , 78 W) The reset times are given by

$$t_{\nu r} = t_{\nu r}^{'} \sqrt{LC} = 4.34 \times 1.16 = 5 \mu s$$

(<20 \mu s)

$t_{\mu r} = t_{\mu r}^{'} \sqrt{LC} = 2.9 \times 1.16 = 3.4 \mu s$  (<5 \mu s)

It is seen that smaller capacitance (0.27  $\mu$ F versus 1.2  $\mu$ F) can be employed if simultaneous *L*-*C* transfer and *R*-*C* discharge are accounted for. The stray inductance of the resistor discharge path has been neglected. Any inductance decreases the effectiveness of the *R*-*C* discharge. Larger *C* than 0.27  $\mu$ F and *R* < 3.3 $\Omega$  are needed, as is now shown.

*ii.* (b)  $L_R = 1\mu$ H, that is,  $L' = L_R/L = 0.2$

In figure 9.7, for a minimum voltage reset time,  $\xi = 0.7$ ,  $V_{cp}' = 0.54$  when the L' = 0.2 curve is used. The normalised reset times are unchanged, that is  $t'_{ir} = 2.9$  and  $t'_{vr} = 4.34$ . Using the same procedure as in part ii b

$$0.54 = \frac{50V}{25A}\sqrt{\frac{5\mu H}{C}} \text{ gives } C = 0.37\mu\text{F} \text{ (use } 0.39\mu\text{F)}$$

$$R = \frac{1}{2\xi}\sqrt{\frac{L}{C}} = \frac{1}{2\times0.7}\sqrt{\frac{5\mu H}{0.39\mu\text{F}}} = 2.6\Omega \text{ (use } 2.7\Omega, 78\text{W)}$$

Since resistor inductance has been accounted for, parallel connection of four  $10\Omega$ , 25W wire-wound aluminium clad resistors can be used.

$$t_{\nu r} = 4.34 \times 1.4 = 6\mu s$$

(< 20 $\mu s$ )

$t_{ir} = 2.90 \times 1.4 = 4\mu s$  (< 5 $\mu s$ )

Note that circuit supply voltage  $V_s$  is not a necessary design parameter, other than to specify the capacitor absolute dc voltage rating. This supply independence is expected since in ac circuit analysis, as is applicable here during the transient snubber operational period, dc voltage sources are shorted.

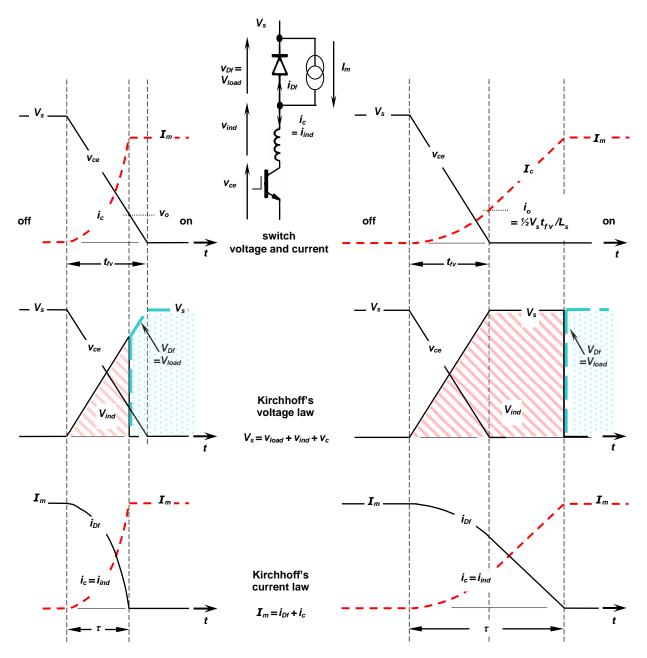

9.3 Polarised switching-aid circuits

Optimal gate drive electrical conditions minimize collector (or drain or anode) switching times, thus minimizing switch electrical stresses and power losses. Proper gate drive techniques greatly enhance the switching robustness and reliability of a power switching device. Switching-aid circuits, commonly called *snubber circuits*, can be employed to further reduce device switching stresses and losses. Optimal gate drive conditions minimise the amount of snubbering needed.

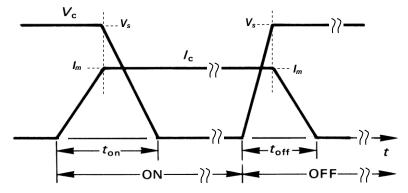

Figure 9.8. Idealised collector (anode) switching waveforms for an inductive load.

During both the switch-on and the switch-off transition intervals, for an inductive load as considered in chapter 7.2, an instant exists when the switch simultaneously supports the supply voltage  $V_s$  and conducts the full load current  $I_m$ , as shown in figure 9.8. The gate drive conditions cannot alter this peak power loss but can vary the duration of the switching periods ( $t_{on}$  and  $t_{off}$ ). From chapter 7, for an inductive load, the switching losses, W, dissipated as heat in the switch, are given by

for turn-on:

$$W_{on} = \frac{1}{2} V_s I_m t_{on}$$

(J)(9.13)for turn-off: $W_{off} = \frac{1}{2} V_s I_m t_{off}$ (J)(9.14)

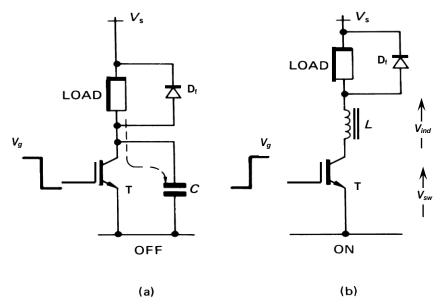

In order to reduce switching losses, two snubber circuits can be employed on a power switching device, one operational during switch turn-on, the other effective during turn-off. In the case of the turn-off snubber, energy (current) is diverted from the switch turning off into a parallel capacitor as shown in figure 9.9a thus the capacitor controls the voltage rise. The turn-on snubber utilises an inductor in series with the collector as shown in figure 9.9b in order to support part of the dc voltage supply as the collector (anode) voltage falls. The inductor therefore controls the rate of rise of collector (anode) current during the collector voltage fall time. For both snubbers, the *I-V* SOA trajectory is modified to be within that area shown in figure 7.8.

- A series inductive turn-on snubber is essential for the GCT and the GTO thyristor in order to control the anode initial di/dt current to safe levels at switch turn-on. In large area thyristor devices, the inductor controlled current increase at turn-on, allows sufficient time for the silicon active area to spread uniformly so as to conduct safely the prospective load current. Special thyristor gate structures such as the amplifying gate, as shown in figure 3.24, allow initial anode di/dt values of up to 1000 A/us. Use of an inductive turn-on snubber with the MOSFET and the IGBT is limited but may be used because of freewheel diode imposed limitations rather than an intrinsic need by the switch.

- The shunt **capacitive turn-off snubber** is used extensively across the GTO thyristor. The *R-D-C* circuit is necessary to ensure that GTO turn-off occurs at a low anode-to-cathode voltage, preventing excessive power loss at the central GTO junction during reverse recovery. Larger area GTOs employ 1 to 8  $\mu$ F in an *R-D-C* turn-off snubber and at high voltages and frequencies the associated losses,  $\frac{1}{2}C_s V_s^2 f_s$ , tend to be high. To reduce this loss, GTOs with an increased SOA, namely GCTs, for use without a turn-off snubber are available. These devices under utilise their voltage and current density capabilities as compared with when used with a turn-off snubber.

While the switching performance of IGBTs and MOSFETs can be enhanced by using the turn-off snubber, it is not a prerequisite for safe, reliable switch operation.

Figure 9.9. Basic switching-aid circuits comprising: (a) a parallel capacitor for current shunting at switch turn-off and (b) a series inductor for supporting voltage, thus limiting the rate of rise of principal current at turn-on.

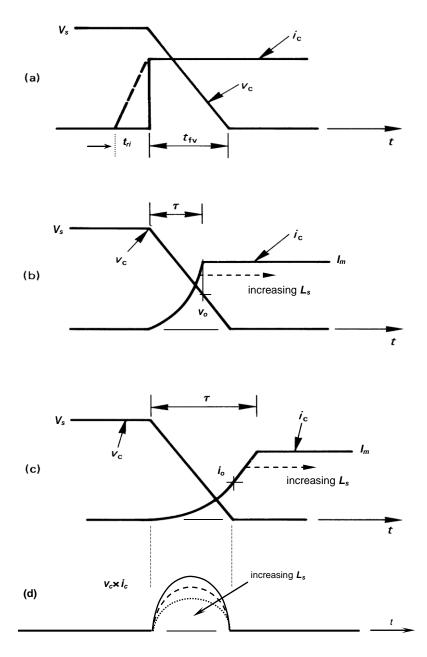

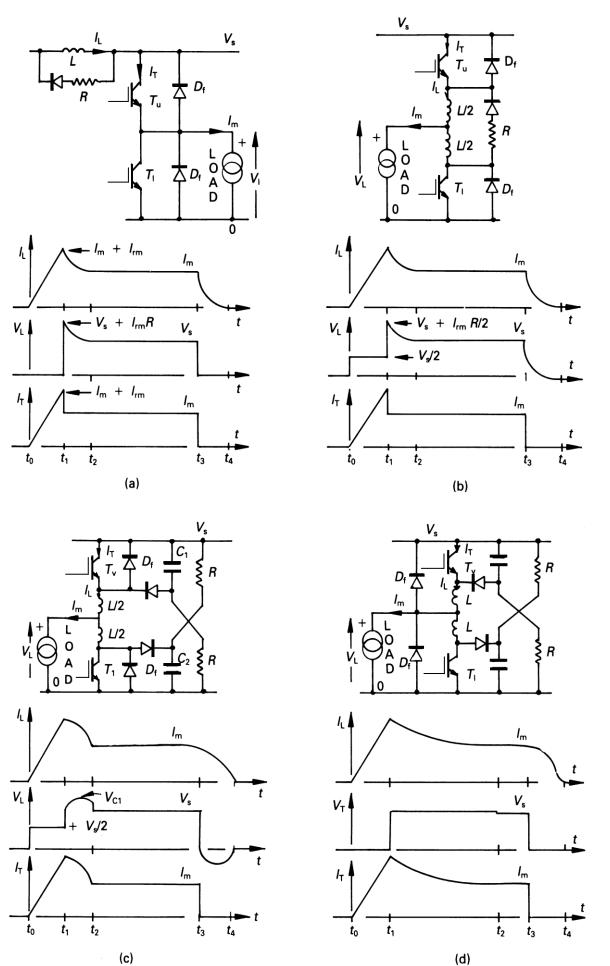

#### 9.3.1 The polarised turn-off snubber circuit - assuming a linear current fall

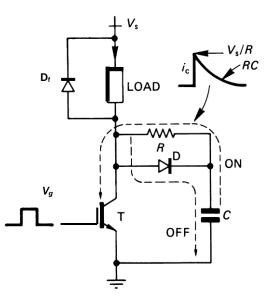

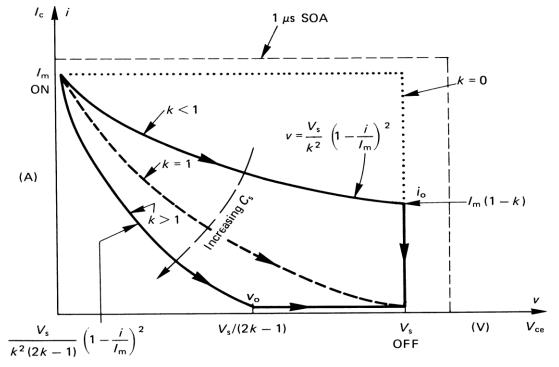

Figure 9.10 shows a complete turn-off snubber circuit comprising a capacitor-diode plus resistor combination across the anode-to-cathode/collector-to-emitter terminals of the switching device. At switch turn-off, load current is diverted into the snubber capacitor *C* via the diode D, while the switch principal current decreases. The anode/collector voltage is clamped to the capacitor voltage, which is initially zero. The larger the capacitor, the slower the anode/collector voltage rises for a given load current and, most importantly, turn-off occurs without a condition of simultaneous supply voltage and maximum load current ( $V_s$ ,  $I_m$ ). Figure 9.11 shows the anode/collector turn-off waveforms for different magnitudes of snubber capacitance. The GTO/IGBT tail current has been neglected, thus the switching device is analysed without any tail current. For clarity, the terminology to be henceforth used, refers to an IGBT, viz., collector, emitter, and gate. Circuit operational explanations equally apply to thyristors.

Figure 9.11a shows turn-off waveforms for a switch without a snubber, where it has been assumed that the collector voltage rise time is short compared with the collector current fall time, which is given by  $i_c(t) = I_m(1 - t / t_n)$ . For low capacitance values, the snubber capacitor (whence collector voltage) may charge to the rail voltage before the collector current has fallen to zero, as seen in figure 9.11b. For larger capacitance, the collector current reaches zero before the capacitor (whence collector voltage) has charged to the rail voltage level, as shown in figure 9.11c.

Figure 9.10. *Practical capacitive turn-off snubber showing capacitor charging and discharging paths during device switching.*

Figure 9.11. Switch turn-off waveforms: (a) unaided turn-off; (b) turn off with small snubber capacitance; (c) turn-off with large snubber capacitance; (d) and switch power losses. For analysis, the collector voltage rise time for an unaided switch is assumed zero. The device switch-off energy losses without a snubber, as shown in figure 9.11a, are given by

$$W = \frac{1}{2}V_s I_m t_{fi}$$

(J) (9.15)

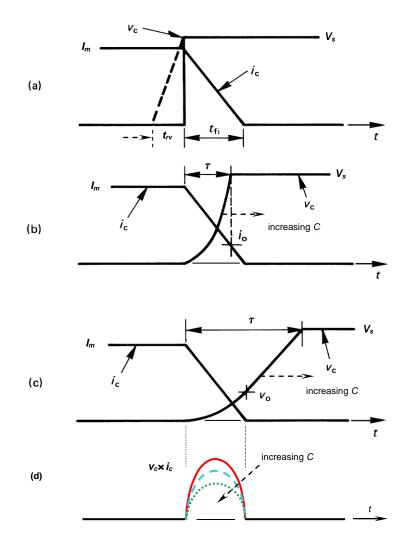

With a snubber circuit, switch losses are decreased as shown in figure 9.11d, but snubber (resistor) losses are incurred. After turn-off the capacitor is charged to the rail voltage. This stored energy,  $\frac{1}{2}C_s V_s^2$ , is subsequently dissipated as heat in the snubber circuit resistor at subsequent switch turn-on, when an *R*-*C* discharge current flows. If the snubber *RC* time constant is significantly shorter than the switch voltage fall time at turn-on, the capacitor energy dissipated in the resistor is less than  $\frac{1}{2}C_s V_s^2$  and switch losses are increased as considered in 9.1.1. A range of capacitance values exists where the total losses - snubber plus switch - are less than those losses incurred if the same device is switched unaided, when losses as given by equation (9.14) result. Two distinct snubber design cases exist, depending on capacitance magnitude, as indicated by figures 9.11b and 9.11c. The two possibilities and the associated circuit voltage and current waveforms in each case are shown in detail in figure 9.12. The waveforms are based on satisfying Kirchhoff's voltage and current laws for each case.

Figure 9.12. Switch turn-off waveforms satisfying Kirchhoff's laws: (a) turn-off with small snubber capacitance and (b) turn-off with large snubber capacitance.

From i = C dv/dt, the snubber capacitor charges according to  $v_c(t) = V_s (t/\tau)^2$ , to  $V_s$  before the collector current has reached zero, thus the switch losses are given by

$$W_{t} = \frac{1}{2}V_{s}I_{m}t_{f}\left(1 - \frac{4}{3}k + \frac{1}{2}k^{2}\right)$$

(J) (9.16)

for  $k \le 1$ , where  $k = \tau/t_{fi}$ , as defined in figures 9.12a and 9.13.

Alternatively, with larger capacitance, if the snubber capacitor charges to  $v_o < V_s$ , according to  $v_c(t) = v_o (t / t_{fi})^2$ , thus not charging to  $V_s$  until after the collector current reaches zero, that is  $k \ge 1$ , then the switch losses are given by

$$W_{t} = \frac{\frac{1}{2}V_{s}I_{m}t_{f}}{6(2k-1)}$$

(J) (9.17)

for  $k \ge 1$  as defined in figures 9.12b and 9.13. Initially the capacitor voltage increase is quadratic, then when the collector current reaches zero, the load current charges the capacitor, hence the voltage increase becomes linear.

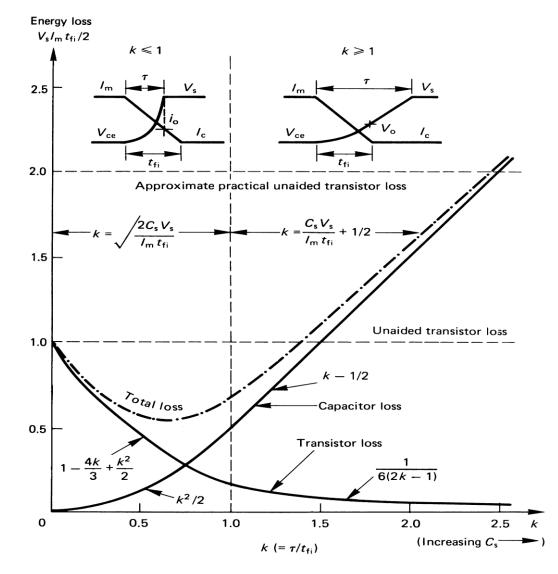

These losses, normalised with respect to the unaided switch losses given by equation (9.15), are plotted in figure 9.13. The switch and capacitor (subsequently resistor) components contributing to the total losses are also shown. A number of points arise concerning turn-off snubbers and snubber losses.

(a) Because of current tailing, voltage overshoot, and the assumption that the voltage rise time  $t_{rv}$  is insignificantly short, practical unaided switch losses, equation (9.14), are approximately twice those indicated by equation (9.15).

(b) As the snubber capacitance increases, that is, k increases, the switch loss is progressively reduced but at the expense of increased snubber associated loss.

(c) If  $k \le 1.41$  the total losses (switch and reset resistor) are less than those for an unaided switch. In the practical case  $k \le 2.70$  would yield the same condition.

Figure 9.13. Loss components for a switch at turn-off when employing a capacitance-type snubber and assuming the collector current falls according to  $i_c = I_m(1-t/t_f)$ .

(d) A minimum total loss (switch plus reset resistor) condition exists. When  $k = \frac{2}{3}$  the total losses are only  $\frac{5}{9}$  those of an unaided switch. The snubber capacitance for this optimal case is given by

$$C_{s} = \frac{2}{9} \frac{I_{m} t_{fi}}{V_{s}}$$

(F) (9.18)

(e) Losses are usually minimised at the switch maximum loss condition, that is maximum load current  $I_m$ . At lower currents, capacitor charging time increases, as is the output voltage distortion. (f) Snubbers not only reduce total losses, but because the loss is distributed between the switch and resistor, more effective heat dispersion can be achieved.

(g) High switch current occurs at turn-on, incorporating the load current  $I_m$ , the snubber capacitor exponential discharge  $\frac{V_s}{R}(1 - e^{-t/\alpha})$ , and any freewheel diode reverse recovery current.

The capacitor energy  $\frac{1}{2}C_{s}V_{s}^{2}$  is removed at turn-on and is exponentially dissipated mainly in the snubber circuit resistor *R*. The power rating of this resistor is independent of resistance but dependent on the maximum switching frequency. The reset resistor power rating is given by

$$P_{R_s} = \frac{1}{2}C_s V_s^2 f_s \qquad (W) \tag{9.19}$$

Two factors specify the snubber discharge circuit resistance value.

- The snubber circuit *RC* time constant period must ensure that after turn-on the capacitor discharges before the next switch turn-off is initiated. If  $\check{t}_{on}$  is the minimum switch on-time, then  $\check{t}_{on} = 5R_sC_s$ , is sufficient to ensure the correct snubber circuit initial conditions, namely, zero capacitor voltage.

- The resistor initial current at capacitor discharge is V<sub>s</sub> / R<sub>s</sub>. This component is added to the load current at switch turn-on, hence adding to the turn-on stresses. The maximum collector current rating must not be exceeded. In order to reduce the initial discharge current, a low valued inductor can be added in series with the resistor, (or a wire-wound resistor used), thus producing an overdamped *L*-*C*-*R* discharge current oscillation at turn-on. Note that the resistor power loss in equation (9.19) is independent of resistance value. The resistance determines the period of time over which the capacitor stored energy is dissipated at switch turn-on.

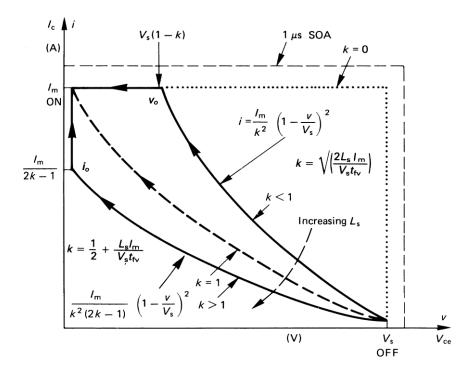

Figure 9.14. The collector I-V trajectory at turn-off with a capacitive switching-aid circuit.

As a result of utilising a capacitive turn-off snubber, the collector trajectory across the SOA is modified as shown in figure 9.14. It is seen that the undesired unaided condition of simultaneous supply voltage  $V_s$  and load current  $I_m$  is avoided. Typical trajectory conditions for a turn-off snubbered device are shown for three situations, depending on the relative magnitudes of  $t_{fi}$  and  $\tau$  (the magnitude of  $C_s$ ). A brief mathematical derivation describing the turn-off switching-aid circuit action is presented in the appendix in section 9.6 at the end of this chapter.

Figure 9.15. Loss components for a switch at switch-off when employing a capacitance-type snubber and assuming a collector fall current according to  $i_c = \frac{1}{2}I_m\{1 + \cos(\pi t/T)\}$ .

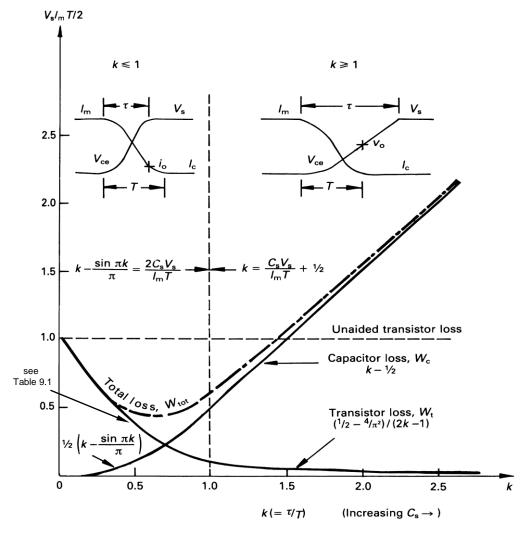

#### 9.3.2 The turn-off snubber circuit - assuming a cosinusoidal current fall

As an alternative to a linear current fall at turn-off, it may be more realistic to assume that the current falls cosinusoidally according to

$$i_c(t) = \frac{1}{2}I_m(1 + \cos \pi t / T)$$

(A) (9.20)

for  $0 \le t \le T$ , as shown in figure 9.15.

As with a linear current fall, two cases exist.

- (i)  $\tau \leq T$  ( $k \leq 1$ ), that is the snubber capacitor charges to  $V_s$  in time  $\tau$ , before the switch current reaches zero, at time T.

- (ii)  $\tau \ge T$  ( $k \ge 1$ ), that is the snubber capacitor charges to the supply  $V_s$  after the switch current has fallen to zero.

These two cases are shown in figure 9.15 where *k* is defined as  $\tau$  /*T*. Using a similar analysis as presented in the appendix (section 9.6), expressions can be derived for switch and snubber resistor losses. These and the total losses for each case are summarised in table 9.1.

Figure 9.15 shows that a minimum total loss occurs, namely

$$W_{total} = 0.41 \times \frac{1}{2} V_s I_m T \quad \text{at} \quad k = 0.62$$

$$C_s = 0.16 \frac{I_m T}{V_s} \qquad (F) \qquad (9.21)$$

when

For  $t_{fi} < 0.85T$ , a cosinusoidal fall current predicts lower total losses than a linear fall current, with losses shown in figure 9.13.

| $\frac{1}{V_{s}I_{m}T/2}$ | $k = \tau/T \leq 1$                                                                                         | $k = \tau/T \ge 1$                                                                               |

|---------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Switch W <sub>t</sub>     | $\frac{k^2}{2} + \frac{2}{\pi^2} (\cos \pi k - 1) + \frac{k}{\pi} \sin \pi k - \frac{\sin^2 \pi k}{2\pi^2}$ | $\frac{1}{2} - \frac{4}{\pi^2}$                                                                  |

|                           | $\left(k-\frac{\sin \pi k}{\pi}\right)$                                                                     | 2k - 1                                                                                           |

|                           | $+1-k-\frac{\sin \pi k}{\pi}$                                                                               |                                                                                                  |

| Resistor W <sub>c</sub>   | $\left(k-\frac{\sin \pi k}{\pi}\right)/2$                                                                   | $k - \frac{1}{2}$                                                                                |

| W <sub>tot</sub>          | $W_{\rm t} + W_{\rm c}$                                                                                     | $\left(k-\frac{1}{2}\right)+\left(\frac{1}{4}-\frac{2}{\pi^2}\right)/\left(k-\frac{1}{2}\right)$ |

#### Table 9.1: Normalised switching loss components at turn-off with a cosinusoidal current fall of half period T

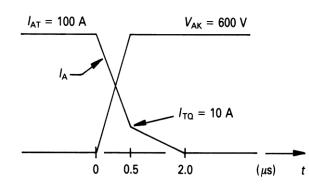

#### **Example 9.4:** Capacitive turn-off snubber design

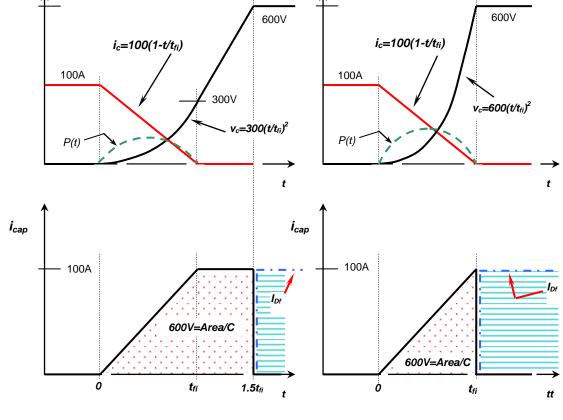

A 600V, 100A machine field winding is switched at 10kHz. In maintaining a constant field current, the switch operates with an on-state duty cycle ranging between 5% and 95% (5%  $\leq \delta \leq$  95%) and has a turn-off linear current fall time of 100ns, that is,  $i_c(t) = 100 \times (1 - t / 100ns)$ .

- *i.* Estimate the turn-off loss in the switch.

- *ii.* Design a capacitive turn-off snubber using the dimensionally correct identity i = Cdv/dt. What is the capacitor voltage when the collector current reaches zero.

- *iii.* Design a capacitive turn-off snubber such that the switch voltage reaches 600V at the same time the conducting current reaches zero.

In each snubber case calculate the percentage decrease in un-aided switch turn-off power dissipation.

#### Solution

*i*. The switch un-aided turn-off losses are given by equation (9.14). The turn-off time is greater than the current fall time (since the voltage rise time  $t_{rv}$  has been neglected), thus the turn-off switching losses will be greater than

$$\begin{split} \mathcal{W}_{off} &= \frac{1}{2} \mathcal{V}_{s} I_{m} t_{off} = \frac{1}{2} \times 600 \text{V} \times 100 \text{A} \times 100 \text{ns} = 3 \text{mJ} \\ \mathcal{P}_{off} &= \mathcal{W}_{off} \times f_{s} = 3 \text{mJ} \times 10 \text{kHz} = 30 \text{W} \end{split}$$

*ii.* Use of the equation i = Cdv/dt results in a switch voltage that reaches the rail voltage after the collector current has fallen to zero. From  $k = \frac{1}{2} + C_s V_s / I_m t_n$  in figure 9.13, k = 3/2 satisfies the dimensionally correct capacitor charging equation. Substitution into i = Cdv/dt gives the snubber capacitance

$$100A = C \frac{600V}{100ns}$$

that is  $C = 16 \frac{2}{3} \text{ nF}$

Use an 18nF, 1000V dc, metallised polypropylene, high *dv/dt* capacitor. The snubber capacitor discharges at switch turn-on, and must discharge during the switch minimum ontime. That is

$$\dot{t}_{on} = 5 CR$$

5% of

$$1/10$$

kHz = 5 ×  $R$  × 18nF

that is

$$R = 55.5\Omega$$

Use  $56\Omega$

The discharge resistor power rating is independent of resistance and is given by

$$P_{56\Omega} = \frac{1}{2}CV_s^2 f_s$$

$$= \frac{1}{2} \times 18 \text{nF} \times 600 \text{V}^2 \times 10 \text{kHz} = 32.4 \text{W}$$

Use 50W.

The resistor can be wire-wound, the internal inductance of which reduces the initial peak current when the capacitor discharges at switch turn-on. The maximum discharge current into the switch during reset, which is added to the 100A load current and any diode reverse recover current, is

$$I_{56\Omega} = V_s / R = 600 V / 56\Omega = 10.7 A$$

which decays exponential to zero in five time constants, 5µs. The peak switch current (neglecting freewheel diode recovery) is 100A+10.7A=110.7A, at turn-on.

At switch turn-off, when the switch current reduces to zero, the snubber capacitor has charged to a voltage less than the 600V rail voltage, specifically

$$v_{0} = \frac{1}{C} \int i_{cap} dt$$

=  $\frac{1}{16\frac{2}{3}} nF \int_{0}^{100ns} 100 \text{A} \times \left(\frac{t}{100 \text{ns}}\right) dt = 300 \text{V}$  (277V with 18nF)

The switch turn-off losses are reduced from 30W to

$$P_{off} = f_s \int_{0}^{100 \text{ns}} i_c v_{ce} dt = f_s \int_{0}^{100 \text{ns}} I_m \left( 1 - \frac{t}{100 \text{ ns}} \right) \times v_0 \left( \frac{t}{100 \text{ ns}} \right)^2 dt$$

$$= f_s \int_{0}^{100 \text{ns}} 100 \text{A} \left( 1 - \frac{t}{100 \text{ ns}} \right) \times 300 \text{V} \left( \frac{t}{100 \text{ ns}} \right)^2 dt = 2.5 \text{W} \qquad (2.3 \text{W with } 18 \text{nF})$$

The total turn-off losses (switch plus snubber resistor) are 2.5W+32.4W=34.9W, which is more than the 30W for the unaided switch. Since the voltage rise time has been neglected in calculating the un-aided losses, 34.9W would be expected to be less than the practical un-aided switch losses. The switch losses have been reduced by  $91\frac{2}{3}$ %, ( $\frac{1}{12}$ ), from 30W to 2.5W.

*iii.* As the current in the switch falls linearly to zero, the capacitor current increases linearly to 100A (k = 1), such that the load current remains constant, 100A. Initially the capacitor voltage increases in a quadratic function according to

$$V_{cap}(t) = \frac{1}{C} \int i_{cap} dt$$

The capacitor charges quadratically towards 600V in 100ns, as its current increases linearly from zero to 100A, that is

$$600V = \frac{1}{C} \int_{0}^{100ns} 100A \frac{t}{100ns} dt$$

that is  $C = 8 \frac{1}{2} nF$

Use a 10nF, 1000V dc, metallised polypropylene, high dv/dt capacitor.

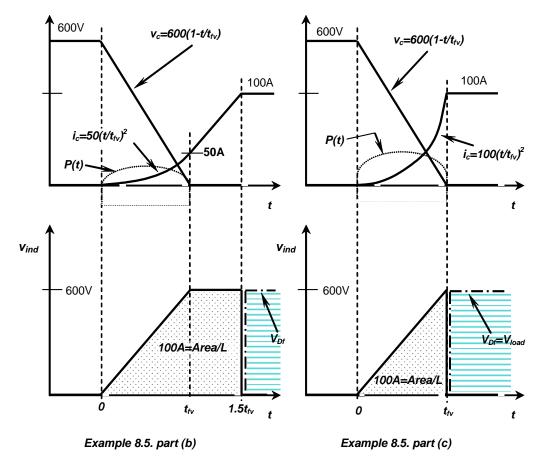

Example 9.4. part (b)

Example 9.4. part (c)

Figure 9.16. Solution to Example 9.4.

The necessary reset resistance to discharge the 10nF capacitor in 5µs is  $5\mu s = 5 \times R \times 10 nF$

that is

$$R = 100\Omega$$

The power dissipated in the reset resistor is

$$P_{100\Omega} = \frac{1}{2}CV_s^2 f_s$$

=  $\frac{1}{2} \times 10$ nF  $\times 600$ V<sup>2</sup>  $\times 10$ kHz = 18W

Use a 100 $\Omega$ , 25W, wire-wound, 600V dc withstand voltage, metal clad resistor.

The resistance determines the initial current magnitude and the period over which the capacitor energy is dissipated. The resistance does not determine the amount of energy dissipated. The capacitor exponentially discharges with an initial current of  $600V/100\Omega = 6A$ , which adds to the 100A load current at switch turn-on. The peak switch current is therefore 100A+6A = 106A, at turn-on.

The energy dissipated in the switch at turn-off is reduced from 30W when un-aided to

$$P_{off} = f_s \int_{0}^{100 \text{ns}} i_c v_c dt = f_s \int_{0}^{100 \text{ns}} I_m \left(1 - \frac{t}{100 \text{ ns}}\right) \times V_s \left(\frac{t}{100 \text{ ns}}\right)^2 dt$$

$$= f_s \int_{0}^{100 \text{ns}} 100 \text{A} \left(1 - \frac{t}{100 \text{ ns}}\right) \times 600 \text{V} \left(\frac{t}{100 \text{ ns}}\right)^2 dt = 5 \text{W} \quad (\text{using 8 } \frac{1}{3} \text{ nF})$$

The total losses (switch plus snubber resistor) with a turn-off snubber are 5W+18W =23W, which is less than the 30W for the unaided switch. The switch loss has been decreased by  $83\frac{1}{3}\%$  ( $\frac{1}{6}$ ), (30W to 5W).

Note that the losses predicted by the equations in figure 9.13 amount to 5W + 15W = 20W. The discrepancy is due to the fact that the preferred value of 10nF with k = 1.2 giving 5W + 18W = 23W (rather that the calculated  $81/_{n}$ F, k = 1) has been used for the resistor loss calculation.

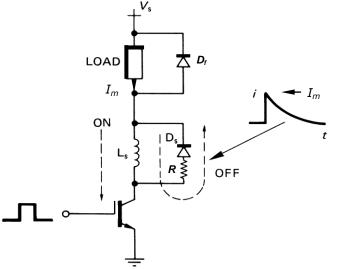

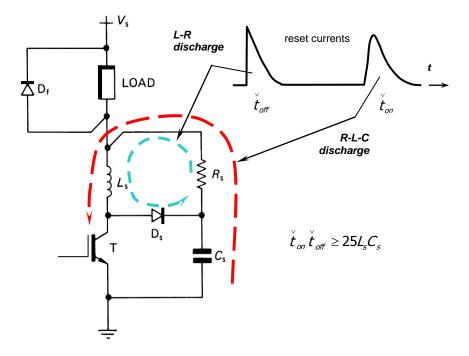

#### 9.3.3 The polarised turn-on snubber circuit – with air-core (non-saturable) inductance

A series turn-on snubber comprises an inductor-diode combination in the collector circuit as shown in figure 9.17. At turn-on the inductor controls the rate of rise (from zero) of collector current and supports a portion of the supply voltage while the collector voltage falls. At switch turn-off the energy stored in the inductor,  $\frac{1}{2}L_sI_m^2$ , is transferred in the form of current through the diode and dissipated in the diode D<sub>s</sub> and any added series resistance R, and in the resistance of the inductor.

Figure 9.17. Turn-on switching-aid circuit incorporating series inductance, L<sub>s</sub>.

Figure 9.18 shows collector turn-on waveforms with and without a turn-on snubber circuit. The turn-on loss associated with an unaided switch, figure 9.18a, neglecting the current rise time, is given by W 9.22)

$$=\frac{1}{2}V_{s}I_{m}t_{fv} \qquad (J)$$

where it is assumed that the collector current rise time is zero and that the collector voltage falls linearly, according to  $v_c(t) = V_s(1-t/t_{fv})$ .

When an inductive turn-on snubber circuit is employed, collector waveforms as in figure 9.18b or 9.18c result.

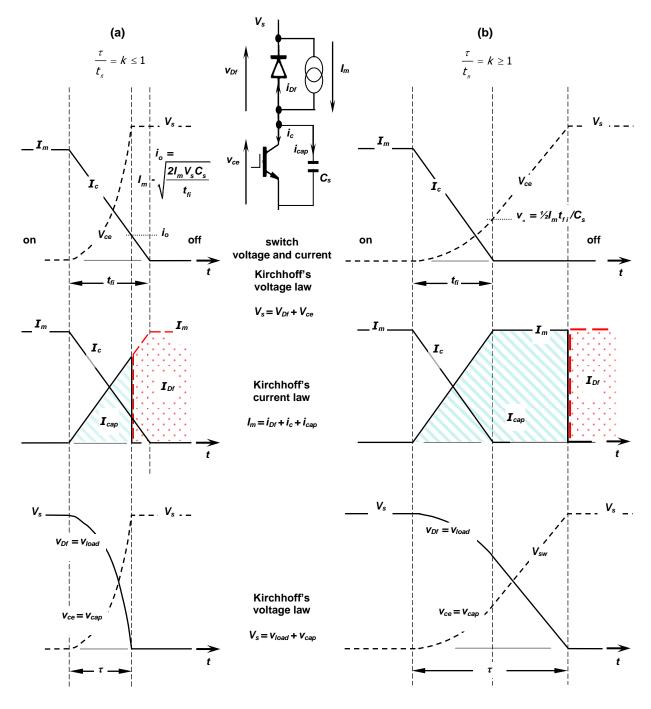

The two possibilities and the associated circuit voltage and current waveforms in each case are shown in detail in figure 9.19. The waveforms are based on satisfying Kirchhoff's voltage and current laws for each case.

For low inductance the collector current reaches its maximum value  $I_m$  (the load current) before the collector voltage has reached zero. As shown in figure 9.18b, from  $v = L \frac{di}{dt}$ , the collector current increases quadratically  $i_c(t) = I_m (t/\tau)^2$  and the switch turn-on loss is given by

$$W_t = \frac{1}{2}V_s I_m t_{\bar{k}} \quad (\frac{1}{2}k^2 - \frac{4}{3}k + 1) \tag{J}$$

for  $k \le 1$ , where  $k = \tau / t_{fv}$  as defined in figure 9.18.

Figure 9.18. Switch voltage and current collector waveforms at turn-on: (a) without a snubber; (b) and (c) with an inductive snubber; and (d) switch power losses.

These losses include both switch losses and stored inductor energy subsequently dissipated. For higher snubber inductance, the collector voltage reaches zero before the collector current reaches the load current level. Initially the inductor current increases quadratically  $i_{Ls}(t) = i_o (t/t_{fv})^2$ , then when the collector voltage has reached zero, the current increases linearly. The switch loss is given by

$$W_t = \frac{1}{2}V_s I_m t_{hv} \frac{1}{6 \times (2k-1)}$$

(J) (9.24)

Note that these equations are similar to those for the turn-off snubber, except that the current fall time  $t_{fi}$  is replace by the voltage fall time,  $t_{fv}$ . The normalised loss components for the capacitive snubber in figure 9.13 are valid for the inductive turn-on snubber.

Figure 9.19. Turn-on snubber waveforms satisfying Kirchhoff's laws: (a) turn-on with small snubber inductance and (b) turn-on with large snubber inductance.

Minimum total turn-on losses of 5/9 those of the un-aided case, occur at  $k = \frac{2}{3}$  when

$$L_{s} = \frac{2}{9} \frac{V_{s} t_{iv}}{I_{m}}$$

(H) (9.25)

At switch turn-off, the snubber inductance stored energy is dissipated as heat in the snubber freewheeling diode path. The maximum power loss magnitude is dependent on the operating frequency and is given by

$$P_{L_s} = \frac{1}{2} L_s I_m^2 f_s$$

(W) (9.26)

This power is dissipated in the inductor winding resistance, resistance *R*, and freewheeling diode  $D_s$ . The time constant is designed such that  $\check{t}_{off} = 5L_s/R$  where  $\check{t}_{off}$  is the minimum device off-time, where *R* is the effective total series resistance. The time constant can be reduced either by increasing the series resistance or by inserting a Zener diode as shown in figure 9.20.

A disadvantage of series resistance R as in figure 9.20a is that the switch collector voltage at turn-off is increased from  $V_s$  to  $V_s + I_m R$ . The resistor must also have low self-inductance in order to allow the collector current to rapidly transfer from the switch to the resistor/diode reset circuit. The advantage of using a Zener diode as in figure 9.20b is that the maximum overvoltage is fixed, independent of the load

current magnitude. For a given maximum overvoltage, the Zener diode absorbs the inductor-stored energy quicker than would a resistor (see example 7.3 and problem 9.9). The advantages of using resistive dissipation are lower costs and more robust heat dissipation properties.

Alternatively the Zener diode can be placed across the switch as shown in figure 9.20c. The power dissipated is increased because of the energy drawn from the supply, through the inductor, during reset. At higher power, the soft voltage clamp shown in figure 9.20d, and considered in section 9.2, can be used. At switch turn-off, the energy stored in  $L_s$ , along with energy from the supply, is transferred and stored in a clamp capacitor. Simultaneously energy is dissipated in R and returned to the supply as the capacitor voltage rises. The advantage of this circuit is that the capacitor affords protection directly across the switch, but with lower loss than a Zener diode as in figure 9.20c. The energy loss equation for each circuit is also shown in figure 9.20. In high-voltage applications, the combined features of the soft clamp in figure 9.20d and the low loss Zener clamp in figure 9.20b can be realised by inserting a series Zener as shown in the figure 9.20d insert. This avoids the need to series connect Zener diodes, which would be necessary if the circuit in figure 9.20c were used at voltages above a few hundred volts.

Figure 9.21 shows how a switch turn-on snubber circuit modifies the SOA trajectory during switch-on, avoiding a condition of simultaneous maximum voltage  $V_s$  and current  $I_m$ .

Figure 9.20. Four turn-on snubber modifications for increasing the rate of release of inductor  $L_s$ stored energy: (a) using a power resistor; (b) using a power Zener diode; (c) parallel switch Zener diode,  $V_z > V_s$ ; and (d) using a soft voltage clamp.

Figure 9.21. The collector I-V trajectory at turn-on with a switching-aid circuit.

#### **Example 9.5:** Turn-on air-core inductor snubber design

A 600V, 100A machine field winding is switched at 10kHz. In maintaining a constant field current, the switch operates with an on-state duty cycle between 5% and 95% (5%  $\leq \delta \leq$  95%) and has a turn-on voltage fall time of 100ns, that is,  $v_c(t) = 600V(1 - t / 100ns)$ .

- *i.* Estimate the turn-on loss of the switch.

- *ii.* Design an inductive turn-on snubber using the dimensionally correct identity v = Ldi/dt. What is the current magnitude in the turn-on inductor when the switch voltage reaches zero.

- *iii.* Design an inductive turn-on snubber such that the switch current reaches 100A at the same time the switch collector voltage reaches zero.

In each snubber case, using first a resistor and second a Zener diode for inductor reset, calculate the percentage decrease in switch power dissipation at turn-on, compared to the un-aided case.

#### Solution

*i*. The switch un-aided turn-on losses are given by equation (9.13). The turn-on time is greater than the voltage fall time (since the current rise time  $t_{ri}$  has been neglected), thus the turn-on switching losses will be greater than

$$W_{on} = \frac{1}{2}V_s I_m t_{on} = \frac{1}{2} \times 600 \text{V} \times 100 \text{A} \times 100 \text{ns} = 3\text{mJ}$$

$$P_{on} = W_{on} \times f_s = 3\text{mJ} \times 10\text{kHz} = 30\text{W}$$

*ii.* Use of the equation v = Ldi/dt results in a switch current that reaches the load current magnitude after the collector voltage has fallen to zero. From  $k = \frac{1}{2} + L_s I_m / V_s t_k$  in figure 9.21, k = 3/2 satisfies the dimensionally correct inductor equation. Substitution into v = Ldi/dt gives the necessary snubber inductance

$$600V = L \frac{100A}{100ns}$$

nat is  $L = 600 \text{ nH}$

The snubber inductor releases its stored energy at switch turn-off, and must discharge (demagnetise) during the switch minimum off-time,  $\check{t}_{off}$ . That is

$$\check{t}_{off} = 5L/R$$

5% of 1/10kHz = 5 × 0.6µH / R

that is  $R = 0.6 \Omega$

Use the preferred value 0.68 $\Omega$  (nearest higher preferred value), which reduces the L/R time constant.

The discharge resistor power rating is independent of resistance and is given by

$$P_{0.68\Omega} = \frac{1}{2}LI_m^2 f_s$$

$$= \frac{1}{2} \times 600 \text{nH} \times 100 \text{A}^2 \times 10 \text{kHz} = 30 \text{W}$$

The resistor in the circuit in figure 9.20a must have low inductance to minimise voltage overshoot at switch turn-off. Parallel connection of metal oxide resistors may be necessary to fulfil both resistance and power rating requirements. The maximum switch over-voltage at turn-off, (assuming zero resistor inductance), at the commencement of core reset, which is added to the supply voltage, 600V, is

$$V_{0.68\Omega} = I_m R = 100 \text{A} \times 0.68 \Omega = 68 \text{V}$$

which decays exponential to zero volts in five time constants,  $5\mu s$ . The maximum switch voltage is 600V + 68V = 668V, at turn-off. The reset resistor should be rated at  $0.68\Omega$ , 30W, metal film, 750V dc working voltage.

A Zener diode, as in figure 9.20b, of  $V_z = LI_m / \check{t}_{off} = 0.6\mu$ H×100A/5 $\mu$ s = 12V, will reset the inductor in the same time as 5 *L/R* time constants. The switch voltage is clamped to 612V during the 5 $\mu$ s inductor reset time at switch turn-off.

At turn-on when the switch voltage reduces to zero, the snubber inductor current (hence switch current) is less than the load current, 100A, specifically

$$i_0 = \frac{1}{L} \int v_{ind} dt$$

$$= \frac{1}{600 \text{nH}} \int_0^{100 \text{ns}} 600 \text{V} \times \left(\frac{t}{100 \text{ns}}\right) dt = 50 \text{A}$$

The switch turn-on loss is reduced from 30W to

$$P_{on} = f_s \int_0^{100 \text{ns}} i_c v_c dt = f_s \int_0^{100 \text{ns}} V_s \left( 1 - \frac{t}{100 \text{ ns}} \right) \times i_0 \left( \frac{t}{100 \text{ ns}} \right)^2 dt$$

$$= f_s \int_0^{100 \text{ns}} 600 \text{V} \left( 1 - \frac{t}{100 \text{ ns}} \right) \times 50 \text{A} \left( \frac{t}{100 \text{ ns}} \right)^2 dt = 2.5 \text{W}$$

The total turn-on losses (switch plus snubber resistor) are 2.5W + 30W = 32.5W, which is more than the 30W for the unaided switch. Since the current rise time  $t_{ri}$  has been neglected in calculating the 30W un-aided turn-on losses, it would be expected that 32.5W would be less than the practical un-aided case. The switch loss is decreased by 92<sup>2</sup>/<sub>3</sub>%, ( $\frac{1}{12}$ ), from 30W down to 2.5W.

Figure 9.22. Solution to Example 8.5.

*iii.* As the voltage across the switch falls linearly to zero from 600V, the series inductor voltage increases linearly to 600V (k = 1), such that the voltage sum of each component adds to 600V. The inductor current increases in a quadratic function according to

$$\dot{V}_{ind}(t) = \frac{1}{L} \int V_{ind} dt$$

The inductor current increases quadratically to 100A in 100ns, as its voltage increases linearly from zero to 600V, that is

$$100A = \frac{1}{L} \int_{0}^{100ns} 600V t/100ns dt$$

that is L = 300nH

The necessary reset resistance to reduce the 300nH inductor current to zero in 5µs is

$$\check{t}_{off} = 5\mu s = 5 \times 0.3\mu H/R$$

that is  $R = 0.3\Omega$

Use the preferred value  $0.33\Omega$  in order to reduce the time constant.

The power dissipated in the  $0.33\Omega$  reset resistor, which is independent of resistance, is

$P_{0.33\Omega} = \frac{1}{2} L I_m^2 f_s = \frac{1}{2} \times 300 \text{nH} \times 100 \text{A}^2 \times 10 \text{kHz} = 15 \text{W}$

The resistance determines the voltage magnitude and the period over which the inductor energy is dissipated, not the amount of inductor energy to be dissipated. The inductor peak reset voltage is  $100A \times 0.33\Omega = 33V$ , which is added to the supply voltage of 600V, giving 633V across the switch at turn-off. That is, use a  $0.33\Omega$ , 15W metal film (for low inductance), 750V dc working voltage resistor.

A Zener diode, as in figure 9.20b, of  $V_z = LI_m / \check{t}_{off} = 0.3 \mu H \times 100 A / 5 \mu s = 6V$  (use 6.8V), will reset the inductor in the same time as 5 *L*/*R* time constants. The switch voltage is clamped to 606.8V during the  $\check{t}_{off} = 5 \mu s$  inductor reset time at turn-off.

The energy dissipated in the switch at turn-on is reduced from 30W to

$$P_{on} = f_s \int_{0}^{100 \text{ns}} i_c v_c dt = f_s \int_{0}^{100 \text{ns}} V_s \left( 1 - \frac{t}{100 \text{ns}} \right) \times I_m \left( \frac{t}{100 \text{ ns}} \right)^2 dt$$

$$= f_s \int_{0}^{100 \text{ns}} 600 \text{V} \left( 1 - \frac{t}{100 \text{ ns}} \right) \times 100 \text{A} \left( \frac{t}{100 \text{ ns}} \right)^2 dt = 5 \text{W}$$

The total turn-on snubber losses (switch plus snubber resistor) are 5W+15W = 20W, which is less than the 30W for the unaided switch. The switch losses, with an inductive turn-on snubber, are decreased by  $83\frac{1}{3}$ %, ( $\frac{1}{6}$ ), from 30W to 5W.

•

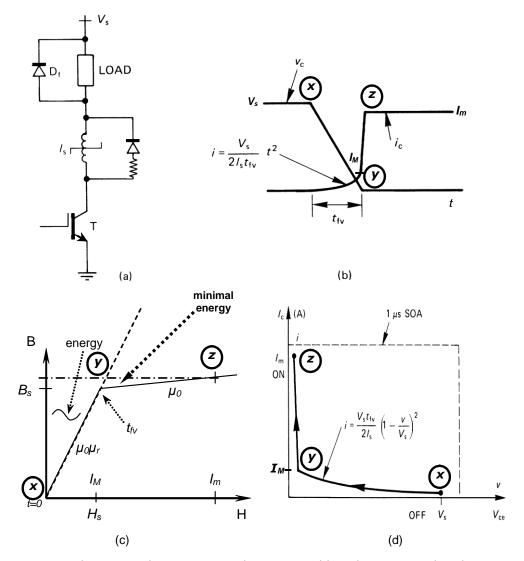

#### 9.3.4 The polarised turn-on snubber circuit - with saturable ferrite inductance

The purpose of a turn-on snubber circuit is to allow the switch collector voltage to fall to zero while the collector current is low. Device turn-on losses are thus reduced, particularly for inductive loads, where during switching the locus point ( $V_s$ ,  $I_m$ ) occurs in the un-aided transition case.

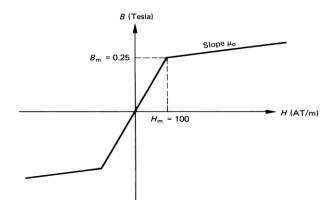

This turn-on loss reduction effect can be achieved with a saturable inductor in the circuit shown in figure 9.23a, rather than using a non-saturable (air core) inductor as previously considered in section 9.3.3. The saturable inductor in the snubber circuit is designed to saturate after the collector voltage has fallen to zero, at point **y** in figure 9.23. Before saturation the saturable inductor presents high reactance and only a low magnetising current flows. Once the collector voltage has reached zero, the inductance can saturate since the switch-on loss period is finished. From Faraday's equation, assuming the collector voltage fall to be linear,  $V_s (1 - t / t_{fv})$ , the saturable inductor  $\ell_s$  must satisfy

$$v_{\ell} = N \frac{d\phi}{dt} = NA \frac{dB}{dt}$$

(9.27)

Rearranging, using an inductor voltage  $V_{\ell}(t) = V_s - V_c(t) = V_s t / t_{fv}$ , and integrating gives

$$B_{s} = \frac{1}{NA} \int_{0}^{t_{f_{v}}} V_{\ell}(t) dt = \frac{1}{NA} \int_{0}^{t_{f_{v}}} V_{s} \frac{t}{t_{f_{v}}} dt$$

(9.28)

which yields the identity

$$V_s = \frac{2NAB_s}{t_{fv}} \qquad (V) \tag{9.29}$$

where *N* is the number of turns,

A is the core area, and

$B_{\rm s}$  is the core ferro-magnetic material saturation flux density.

The inductor magnetising current  $I_M$  should be much less than the load current magnitude  $I_m$ ,  $I_M \ll I_m$ , and the magnetising current at saturation is given by

$$T_{M} = H_{s} L_{eff} / N \tag{(9.30)}$$

where  $L_{eff}$  is the core effective flux path length and  $H_s$  is the magnetic flux intensity at the onset of saturation. Before core saturation the inductance is given by

$$L = N\Phi / I = N^{2} / \Re = \mu_{0} \mu_{r} A N^{2} / L_{eff}$$

(H) (9.31)

When the core saturates the inductance falls to that of an air core inductor ( $\mu_r = 1$ ) of the same turns and dimensions, that is, the incremental inductance is

$$L_{sat} = \mu_0 A N^2 / L_{eff} \tag{H}$$

(9.32)

The energy stored in the inductor core is related to the triangular *B-H* area shown in figure 9.23c and magnetic volume, and is approximated by

$$W_{l_s} = \frac{1}{2}B_s H_s A L_{eff} = \frac{1}{2}LI_M^2$$

(J) (9.33)

The collector turn-on waveforms are shown in figure 9.23b, while the corresponding *B-H* curve and SOA trajectories are illustrated in figure 9.23 parts c and d. It will be seen in figure 9.23b that little device turn-on electrical stressing occurs.

Figure 9.23. Switch turn-on characteristics when a saturable inductor is used in the turn-on snubber: (a) circuit diagram; (b) collector voltage and current waveforms;

(c) magnetic core B-H curve trajectory; and (d) safe operating area I-V turn-on trajectory.

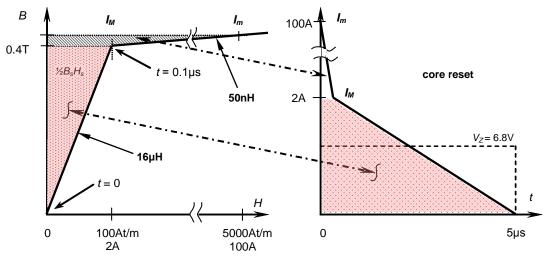

#### Example 9.6: Turn-on ferrite-core inductor snubber design

A 600V, 100A machine field winding is switched at 10kHz. In maintaining the field current constant, the switch operates with an on-state duty cycle between 5% and 95% (5%  $\leq \delta \leq$  95%) and has a turn-on voltage fall time of  $t_{v}$  = 100ns, that is,  $v_c(t) = 600V \times (1 - t/100$ ns).

- *i.* Design a saturable inductor turn-on snubber that saturates as the collector voltage reaches zero, using a ferrite core with the following parameters.

- A = 0.4 sq cm

- *L* = 4cm

- B<sub>s</sub> = 0.4T

- $H_{\rm s} = 100 \,{\rm At/m}$

- *ii.* Calculate the switch losses at turn-on when using the saturable reactor. What is the percentage reduction in switch turn-on losses?

- *iii.* If an air cored inductor is used to give the same switch turn-on loss, what are the losses at reset?

#### Solution

From *example 9.5*, which utilises equation (9.13), the unaided switch turn-on loss is 30W.

i. From equation (9.29) the number of core turns is

$$N = \frac{1}{2}V_s t_{fv} / AB_s$$

$$= \frac{1}{2} \times 600V \times 0.1 \mu s / 0.4 \times 10^{-4} \times 0.4T \approx 2 turns$$

The collector current hence magnetising current  $I_M$  at saturation, that is, when the collector voltages reaches zero, is given by equation (9.30)

$$I_{M} = H_{s} L_{eff} / N$$

= 100At/m × 0.04 / 2 = 2A

Since  $I_M \ll I_m$ , (2A << 100A), this core with 2 turns produces satisfactory turn-on snubber action, resulting in greatly reduced switch losses at turn-on.

From equation (9.31) the inductance before saturation is

$L = NAB_{s} / I_{M}$

$= 2 \times 0.4 \times 10^{-4} \times 0.4 T / 2A = 16 \mu H$

The incremental inductance after saturation, from equation (9.32), is given by

$L_{sat} = N^2 A \mu_0 / L_{eff}$

$$= 2^2 \times 0.4 \times 10^{-4} \times 4\pi \times 10^{-7} / 0.04 = 50$$

nH

From equation (9.33) the energy stored in the core and released as heat in the reset resistor is

$$W_{L} = \frac{1}{2}LI_{M}^{2} \quad (=\frac{1}{2}B_{s}H_{s}L_{eff}A)$$

$$=\frac{1}{2}\times16\mu\text{H}\times2^{2}=32\mu\text{J}$$

$$P_{L} = W_{L} \times f_{s} = 32 \mu J \times 10 kHz = 0.32W$$

The time  $\check{t}_{off}$  for core reset via the resistor in five *L/R* time constants, is dominated by the 16µH section (the pre-saturation section) of the *B*-*H* curve, thus

$$\check{t}_{_{off}} = 5\mu s = 5 \times 16\mu H / R$$

that is  $R = 16\Omega$

Use a  $18\Omega$ , 1W, carbon composition resistor, for low inductance.

This resistance results in a switch voltage increase above 600V of  $18\Omega \times 100A = 1800V$  at turn-off. This high-voltage may be impractical in terms of the switch and resistor voltage ratings.

Alternatively, the Zener diode clamps shown in figures 9.20 b or c, may be suitable to dissipate the 0.32W of stored magnetic energy. The Zener voltage is determined by assuming that a fixed Zener voltage results in a linear decrease in current from 2A to zero in 5µs. That is, assuming minimal core stored energy associated with the current decrease from 100A to 2A,

$$W_{L} = V_{Z} \int_{0}^{t_{off}} i_{ind} dt \quad \left(= \frac{1}{2} L I_{M}^{2}\right)$$

$$32\mu J = \frac{1}{2} \times V_{Z} \times 2A \times 5\mu s$$

that is  $V_7 = 6.4V$

Use a 6.8V, 1W Zener diode to clamp and dissipate the 0.32W of reset power, as in figure 9.20b. Series connected Zener diodes in parallel with the switch, as in figure 9.20c, dissipate 30W.

The energy associated with the saturation region is small and is released in an insignificant time compared to the 5µs minimum off-time. The advantage of the Zener diode clamping approach, as opposed to using a resistor, is that the maximum switch voltage is clamped to 606.8V, even during the short, low energy period when the inductor current falls from 100A to 2A.

ii. The switch turn-on losses with the saturable reactor are given by

$$P_{on} = f_s \int_0^{100 \text{ns}} i_c v_c dt = f_s \int_0^{100 \text{ns}} V_s \left(1 - \frac{t}{100 \text{ns}}\right) \times I_M \left(\frac{t}{100 \text{ ns}}\right)^2 dt$$

$$= f_s \int_0^{100 \text{ns}} 600 \text{V} \left(1 - \frac{t}{100 \text{ ns}}\right) \times 2\text{A} \left(\frac{t}{100 \text{ ns}}\right)^2 dt = 0.1 \text{W}$$

The switch losses at turn-on have been reduced from 30W to 0.1W, a  $99\frac{2}{3}$ % decrease in losses. The total losses (switch plus Zener diode) are 0.1W + 0.32W = 0.42W, which is significantly less than the 30W in the un-aided case.

Figure 9.24. Solution to Example 8.6.

iii. If an air core inductor of  $16\mu$ H (from part i) were to replace the saturable reactor, the stored energy released would give losses

$$W = \frac{1}{2}LI_m^2$$

=  $\frac{1}{2} \times 16\mu H \times 100^2 = 80mJ$

$$P = W \times f_s = 80mJ \times 10kHz = 800W$$

Clearly the use of an air cored inductor rather than a saturable reactor, to achieve the same switch loss of 0.1W at turn-on, is impractical.

#### 9.3.5 The unified turn-on and turn-off snubber circuit

Figure 9.25 shows a switching circuit which incorporates both an inductor turn-on and a capacitor turnoff snubber circuit. Both  $C_s$  and  $L_s$  are dimensioned by the analysis outlined in sections 9.3.1 and 9.3.3, respectively. The power rating of the dissipating resistor R incorporates a contribution from both the turn-on inductor  $L_s$  and turn-off capacitor  $C_s$ , according to

$$P_{R_s} = \frac{1}{2} \left( L_s I_m^2 + C_s V_s^2 \right) f_s$$

(W) (9.34)

Calculated resistance values to satisfy both minimum off and on time reset according to  $\check{t}_{on} \ge 5R_sC_s$  and  $\check{t}_{off} \ge 5L_s/R_s$ , may result in irreconcilable resistance and/or switch voltage/current requirements. The snubber capacitor discharges at turn-on via an *L*-*C*-*R* circuit rather than the usual *R*-*C* circuit, hence reducing the turn-on current stressing of the switch.

In example 9.4 the resistor requirement for the 16<sup>3</sup>/<sub>3</sub>nF capacitive turn-off snubber is  $R < 56\Omega$ , while the 0.6µH inductive turn-on snubber in example 9.5 requires  $R > 0.68 \Omega$ . Thus  $0.68\Omega < R < 56\Omega$  satisfies snubber  $L_s$  and  $C_s$  reset requirements. The maximum reset current and voltage are related to  $Z = \sqrt{L_s/C_s}$ . In combining the two snubber functions, the single resistor may reduce the maximum switch overvoltage at turn-off,  $I_m \times Z$ , and the maximum switch snubber current at turn-on  $V_s /Z$ . If R is too small a high switch snubber current  $V_s /Z$  flows at turn-on, while if R is too large, a large switch over-voltage,  $I_m \times Z$ , occurs at switch turn-off.

An important by-product from using a turn-on snubber circuit is that the inductor controls the reverse recovery process of the load freewheeling bipolar Si diode at switch turn-on.

Figure 9.25. Unified snubber incorporating both a turn-on and a turn-off circuit which share the one dissipation reset resistor.

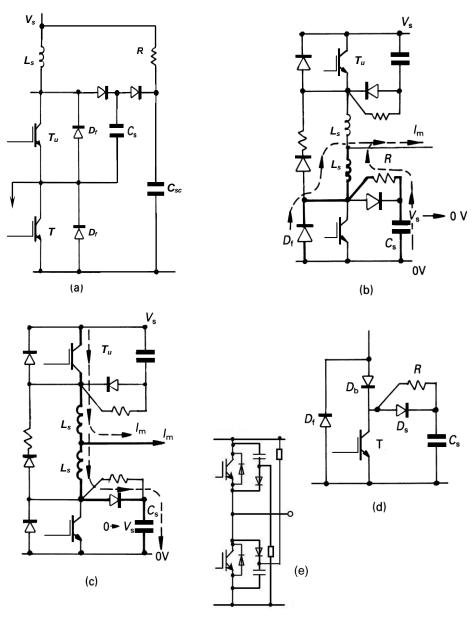

#### 9.4 Snubbers for bridge legs

Figure 9.26 parts a to c show three typical switch bridge leg configurations used in inverters as shown in figures 17.1 and 17.3. The polarised inductive turn-on snubber  $L_s$  and capacitive turn-off snubber  $C_s$  are incorporated into the bridge legs as shown in each circuit in figure 9.26.

The combinational polarised snubber circuit in figure 9.26a can be used to minimise the number of snubber components. The turn-on snubber inductance  $L_s$ , reset resistor R, and snubber capacitor  $C_{sc}$ , are common to any number of bridge legs. The major disadvantage is that turn-off snubber action associated with the lower switch is indirect, relying on low inductance decoupling of  $C_s$  through  $C_{sc}$ .

With an inductive load, unwanted turn-off snubber action occurs during the switch modulation sequence as shown by the paths in figures 9.26b and 9.26c. When the upper switch  $T_u$  is turned off as in figure 9.26b the load current  $I_m$  is diverted to the freewheel diode  $D_f$ . While  $D_f$  conducts, the capacitor  $C_s$ discharges to zero through the resistor R, as shown, dissipating energy  $\frac{1}{2}C_sV_s^2$ . When the switch  $T_u$  is turned on, the load current is provided via the switch  $T_u$  and the snubber capacitor  $C_s$  is charged through the series turn-on snubber inductance, as shown in figure 9.26c. A lightly damped *L*-*C* oscillation occurs and  $C_s$  is over charged. Advantageously, the recovery voltage of the freewheel diode  $D_f$  is controlled by the capacitor voltage rise.

The unwanted snubber action across the non-power conducting switch can be avoided in some applications by using a series blocking diode as shown in figure 9.26d. The diode  $D_b$  prevents  $C_s$  from discharging into the load as occurs with the lower switch in figure 9.26b. A blocking diode can be used to effectively disable the internal parasitic diode of the MOSFET. Adversely, the blocking diode increases the on-state losses.

In reactive load applications, bridge legs are operated with one switch on, with only a short underlap when both switches are off. Thus although the snubber capacitor cannot discharge into the load in figure 9.26d, it always discharges through the switch T, regardless of load current flow through the switch.

A dual soft-clamping circuit is shown in figure 9.26e, which is only active when the switch voltage exceeds the supply voltage and during diode recovery voltage snap overshoot.

In IGBT and MOSFET applications, the conventional *R-C-D* turn-off snubber is not usually required. But because of diode recovery limitations, a turn-on snubber may be necessary. In low frequency applications, a single turn-on snubber inductor can be used in the dc link as shown in figure 9.27a. Snubber circuit design is based on the turn-on snubber presented in 9.3.3. The circuit in figure 9.27b is based on the conventional turn-on snubber being incorporated within the bridge leg. Figures 9.27c and d show turn-on snubbers which use the soft voltage clamp, presented in 9.2, to reset the snubber inductor current to zero at turn-off.

Figure 9.26. Bridge leg configurations: (a) Undeland indirect leg snubber circuit; (b) leg with turn-on snubber and turn-off snubber C<sub>s</sub> discharge path shown; (c) L-C oscillation at switch-on;

(d) blocking circuit to prevent snubber capacitor discharge when D<sub>f</sub> conducts; and

(e) dual soft voltage clamps for high current single switch modules.

In each circuit in figure 9.27, at switch turn-off,  $t_3$ , the energy  $\frac{1}{2}LI_m^2$  stored in the turn-on snubber inductor is dissipated in the resistor of the discharge circuit. The energy  $\frac{1}{2}LI_{rm}^2$  in *L*, due to diode recovery, is dissipated in the resistor at time  $t_1$ , in circuits (a), (b) and (c). In figure 9.27d the energy in excess of that associated with the load,  $\frac{1}{2}LI_m^2$ , due to diode recovery, is dissipated in the switch and its parallel connected diode. At time  $t_1$

$$W = V_2 L I_{rm}^2 + \frac{V_{ce}}{V_{ce} + V_{Df}} L I_{rm} I_m$$

(9.35)

is dissipated in the two semiconductor components. Since the energy is released into a low voltage  $v_{ce}$  +  $v_{Df}$ , the reset time  $t_2$  -  $t_1$  is large.

Magnetic coupling of the inductors in figures 9.27c and d does not result in any net energy savings.

Figure 9.27. Turn-on snubbers for bridge legs: (a) single inductor in dc link; (b) unified L-R-D snubber; (c) soft voltage clamp; and (d) soft voltage clamp with load clamped.

#### 9.5 Appendix: Non-polarised turn-off *R-C* snubber circuit analysis

When a step input voltage is applied to the *L*-*C*-*R* circuit in figure 9.3, a ramped voltage appears across the *R*-*C* part of the circuit. If this dv/dt is too large, a thyristor in the off-state will turn on as a result of the induced central junction displacement current, which causes carrier injection from the outer junctions.

The differential equations describing circuit current operation are

$$(D^{2} + 2\xi_{0}D + \omega_{0}^{2})I = 0$$

(9.36)

and

and

$$(\tau D + 1)I = CDe_0 \tag{9.37}$$

where D = differential operator = d/dt

$\xi$  = damping ratio =  $\frac{1}{2}R\sqrt{C/L}$  $\omega_0$  = natural frequency =  $1/\sqrt{LC}$  $\omega$  = oscillation frequency =  $\omega_0\sqrt{1-\xi^2}$

Solution of equations (9.36) and (9.37), for initial current  $I_o = 0$ , leads to

(a) The snubber current

$$I(t) = \frac{e_s}{R} \frac{2\xi}{\sqrt{1-\xi^2}} e^{-\xi\omega_0 t} \sin \omega t \qquad (A)$$

(b) The rate of change of snubber current

$$\frac{dI}{dt} = \frac{e_s}{L} e^{-\xi\omega_0 t} \left( \cos \omega t - \frac{\xi}{\sqrt{1-\xi^2}} \sin \omega t \right)$$

(A/s) (9.39)

(c) Snubber *R*-*C* voltage

$$\boldsymbol{e}_{0} = \boldsymbol{e}_{s} \left( 1 - \boldsymbol{e}^{-\boldsymbol{\xi}\boldsymbol{\omega}_{0}t} \left\{ \cos \boldsymbol{\omega}t - \boldsymbol{\xi}^{\boldsymbol{\xi}} / \sqrt{1 - \boldsymbol{\xi}^{2}} \sin \boldsymbol{\omega}t \right\} \right)$$

(V) (9.40)

(d) The rate of change of R-C voltage

$$\frac{de_0}{dt} = \omega_0 e_s \ e^{-\xi a_0 t} \left( 2\xi \ \cos \omega t \ + \frac{1 - 2\xi^2}{\sqrt{1 - \xi^2}} \ \sin \omega t \right) \qquad (V/s)$$

(9.41)

The maximum value expressions for each equation can be found by differentiation

(a) Maximum snubber current

$$I_{\rho} = \frac{e_{s}}{R} 2\xi e^{\left(-\xi \cos^{-1}\xi/\sqrt{1-\xi^{2}}\right)}$$

(A) (9.42)

when  $\cos \omega t = \xi$

(b) The maximum snubber *di/dt* is given by

$$\frac{dI_{\rho}}{dt} = \frac{e_s - e_0}{L} \tag{A/s}$$

(c) Maximum *R*-*C* voltage

$$\hat{e}_{o} = e_{s} \left( 1 + e^{\left[ -\xi \cos^{-1}\left(2\xi^{2}-1\right)/\sqrt{1-\xi^{2}}\right]} \right)$$

(V) (9.44)

when  $\cos \omega t = 2\xi^2 - 1$

(d) Maximum slew rate,  $\frac{de_0}{dt} = \hat{S}$ for  $\xi < \frac{1}{2}$  $\hat{S} = e_0 \omega_0 e^{\left[-\xi \cos^{-1} \xi \left(3-4\xi^2\right)/\sqrt{1-\xi^2}\right]}$  (V/s) (9.45)

when  $\cos \omega = \xi (3-4\xi^2)$ . The minimum value of the maximum slew rate is 0.81 pu at  $\xi = 0.265$ .

at

$$\xi = \frac{1}{2}$$

,  $\hat{S} = \omega_o e_s$ .

for  $\xi > \frac{1}{2}$

$\hat{S} = 2\xi e_s w_0$  (=  $e_s R / L$ ) (V/s) (9.46)

when  $t = 0$

Equations (9.42) to (9.46), after normalisation are shown plotted in figure 9.4 as a function of the snubber circuit damping factor  $\xi$ . The power dissipated in the resistor is approximately  $C e_s^2 f_s$ .

#### 9.6 Appendix: Polarised turn-off *R-C-D* switching aid circuit analysis

Switch turn-off loss for an unaided switch, assuming the collector voltage rise time is negligible compared with the collector current fall time, is

$$W = \frac{1}{2}V_s I_m t_{fi} \tag{9.47}$$

If *r* is the time in figure 9.11 for the snubber capacitor  $C_s$  to charge to the supply  $V_s$ , and  $t_{fi}$  is the switch collector current fall time, assumed linear such that  $i_c(t) = I_m$  (1-  $t / t_{fi}$ ), then two capacitor charging conditions can exist

•

$$\tau \leq t_{fi}$$

•

$$\tau \ge t_{f_1}$$

Let  $k = \tau/t_{fi}$  and electrical energy  $W = \int_{0}^{t} v i dt$

**Case 1**:  $\tau \le t_{fi}$ ,  $k \le 1$