# CHAPTER 2

# The pn Junction

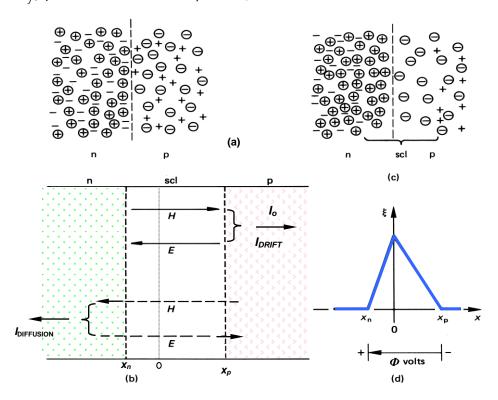

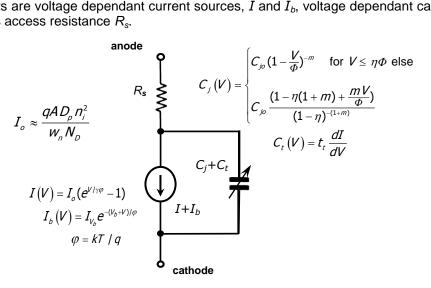

The diode is the simplest bipolar semiconductor device. It comprises p-type and n-type semiconductor materials brought together, usually after diffusion or implantation, to form a (step or abrupt) junction as shown in figures 2.1a and 2.3a.

A *depletion layer*, or alternatively a *space charge layer*, scl, is built up at the junction as a result of diffusion caused by the large carrier concentration gradients. The holes diffuse from the p-side into the n-side while electrons diffuse from the n-side to the p-side, as shown in figure 2.1b. The n-side, losing electrons, is charged positively because of the net donor charge left behind, while the p-side conversely becomes negatively charged. An electric potential barrier,  $\xi$ , builds up, creating a drift current which opposes the diffusion flow, both of which balance at thermo-dynamic equilibrium as shown in figure 2.1c. The electric field is a maximum at the junction and zero at the scl edges. There are no free carriers in the scl.

The zero external bias, built-in, junction potential or scl potential is given by

$$\Phi = \frac{kT_j}{q} \ln \frac{N_A N_D}{n_i^2} \tag{V}$$

where q is the electron charge, 1.6 x 10 <sup>-19</sup> C k is Boltzmann's constant, 1.38 x 10<sup>-23</sup> J/K  $T_j$  is the junction temperature, K.

Thus  $\Phi = kT_i / q = 0.0259 \text{ eV}$  at room temperature, 300 K.

Figure 2.1. The step junction: (a) the junction if carriers did not diffuse:  $\bigoplus$  ionised donors,  $\bigcirc$  ionised acceptors, + holes and - electrons; (b) electron and hole movements: ---- diffusion flow, ——drift flow; (c) ionised impurities and free carriers equilibrium distribution; and (d) scl electric field and voltage.

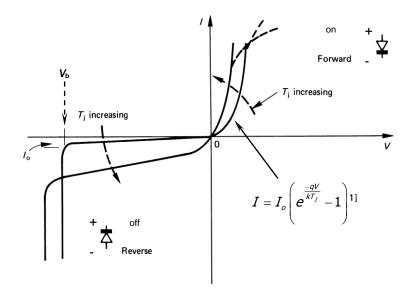

One important feature of the pn junction is that current (holes) flows freely in the p to n direction when forward-biased, that is, the p-region is biased positive with respect to the n-region. Only a small leakage current flows in the reverse voltage bias case. This asymmetry makes the pn junction diode useful as a rectifier, exhibiting static current-voltage I-V characteristics as illustrated in figure 2.2.

Figure 2.2. Typical I-V static characteristics of a silicon pn junction diode, and the effects of junction temperature,  $T_i$ .

# Example 2.1: Built-in potential of an abrupt junction

A silicon abrupt p-n junction has a p-type region of  $2x10^{16}$  cm<sup>-3</sup> acceptors and an n-type region containing  $2x10^{16}$  cm<sup>-3</sup> acceptors in addition to  $10^{17}$  cm<sup>-3</sup> donors.

#### Calculate

- *i.* the thermal equilibrium density of electrons and holes in the p-type region, and both densities in the n-type region

- ii. the built-in potential of the p-n junction at room temperature

- iii. the built-in potential of the p-n junction at 400K, assuming the intrinsic concentration increases 300 fold over that at 300K

#### Solution

i. The thermal equilibrium densities, using  $n_i^2 = p \times n$  from Chapter 1, are:

in the p-type region

$$p = N_A = 2 \times 10^{16} \text{ cm}^{-3}$$

$$n = \frac{n_i^2}{p} = \frac{(1.5 \times 10^{10})^2}{2 \times 10^{16} \text{ cm}^3} = 1.125 \times 10^3 \text{ cm}^{-3}$$

in the n-type region

$$n = N_D - N_A = 8 \times 10^{16} \text{ cm}^{-3}$$

$$p = \frac{n_i^2}{n} = \frac{\left(1.5 \times 10^{10}\right)^2}{8 \times 10^{16} \text{ cm}^3} = 2.813 \times 10^3 \text{ cm}^{-3}$$

ii. The built-in potential at room temperature from equation (2.1) is

$$\Phi = \frac{kT_j}{q} \ln \frac{p_n n_p}{n_i^2} = 0.0259 \text{V} \times \ln \left( \frac{2 \times 10^{16} \times 8 \times 10^{16}}{\left( 1.5 \times 10^{10} \right)^2} \right) = 0.766 \text{V}$$

The intrinsic carrier density is temperature dependant, and increases to 300 x 1.5x10<sup>10</sup> = 4.5x10<sup>12</sup> at 400K. The built-in potential at 400K is

$$\Phi = \frac{kT_j}{q} \ell n \frac{p_n n_p}{n_i^2} = 0.0259 \text{V} \times \frac{400 \text{K}}{300 \text{K}} \times \ell n \left( \frac{2 \times 10^{16} \times 8 \times 10^{16}}{\left( 4.5 \times 10^{12} \right)^2} \right) = 0.630 \text{V}$$

# 2.1 The pn Junction under forward bias (steady-state)

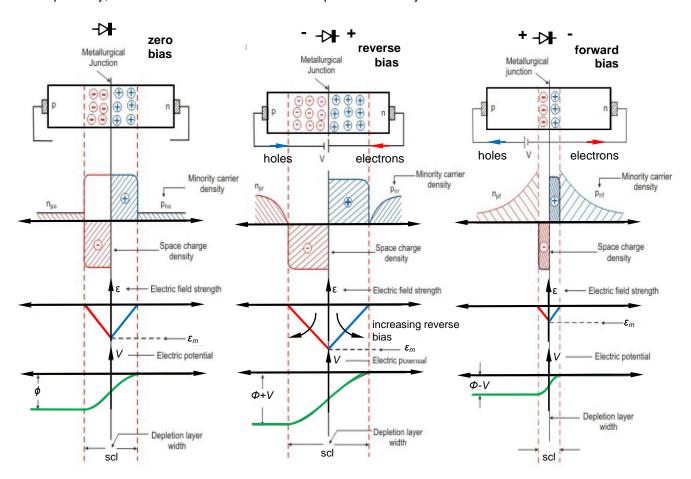

If the p-region is externally positively-biased with respect to the n-region as shown in figure 2.3b, the scl narrows and current flows freely. The emf positive potential supplies holes to the p-region, while the negative emf potential provides electrons to the n-region. The carriers both combine, but are continuously replenished from the emf source. A large emf source current flows through the diode, which is termed *forward-biased*.

# 2.2 The pn junction under reverse bias (steady-state)

If a bias voltage is applied across the p and n regions as shown in figure 2.3c, with the p-terminal negative with respect to the n-terminal, then the neutral scl widens. This is because electrons in the n-region are attracted to the positive external emf source while holes in the p-region are attracted to the negative emf potential. As the scl widens, the peak electric field  $\xi_m$  at the junction increases as shown in figure 2.3d. The only current that flows is the small *leakage current* which is due to carriers generated in the scl or minority carriers which diffuse to the junction and are collected. The junction condition is termed *reverse-biased*.

Increasing applied reverse bias eventually leads to junction reverse voltage breakdown,  $V_b$ , as shown in figure 2.2 (third quadrant), and the diode current is controlled (limited) by the external circuit. Junction breakdown is due to one of three phenomena, depending on the doping levels of the regions and, most importantly, on the concentration of the lower doped side of the junction.

Figure 2.3. Diagrammatic representation of a pn junction diode showing minority carrier flow:

(a) without external applied voltage; (b) with reverse applied voltage; and

(c) with forward applied voltage.

#### 2.2.1 Punch-through voltage

The reverse voltage extends the scl to at least one of the ohmic contacts and the device presents a short circuit to that voltage in excess of the *punch-through* voltage,  $V_{PT}$ . Punch-through tends to occur at low temperatures with devices which employ a low concentration region (usually the n-side), as is usual with high-voltage devices. The punch-through voltage for silicon can be approximated by

$$V_{PT} = 7.67 \times 10^{-16} N_c W_c^2 \tag{V}$$

where

$N_c$  is the concentration in /cc of the lighter doped region and  $W_c$  is the width of that region in  $\mu$ m.

#### 2.2.2 Avalanche breakdown

Avalanche breakdown or multiplication breakdown, is the most common mode of breakdown and occurs when the peak electric field,  $\xi_m$  in the scl at the junction exceeds a certain level which is dependent on the doping level of the lighter doped region. Minority carriers associated with the leakage current are accelerated to kinetic energies high enough for them to ionise silicon atoms on collision, thereby creating a new hole-electron pair. These are accelerated in opposite directions, because of the high electric field strength, colliding and ionising repeatedly - hence the term avalanche, impact ionisation or carrier multiplication. If the lighter doped silicon region has a concentration of

$$10^{13} < N_c < 5 \times 10^{14}$$

(/cc)

then the avalanche voltage may be approximated by

$$V_b = 5.34 \times 10^{13} N_c^{-3/4}$$

(V)

The peak electric field at the junction will be

$$\xi_h = 3.91 \times 10^5 N_c^{1/8}$$

(V/m) (2.4)

and the width of the scl, mainly in the lighter doped region, at breakdown is given by

$$W_{scl} = 2 V_b / \xi_b$$

= 2.73 × 10<sup>8</sup>  $N_c^{-7/8}$  ( $\approx 1 \times 10^{-14} V_b$ ) (m)

#### 2.2.3 Zener breakdown

Field or Zener breakdown occurs with heavily doped junction regions and at usually less than 5V reverse bias. It occurs when the scl is too narrow for avalanche yet the electric field grows very large and electrons tunnel directly from the valence band on the p-side to the conduction band on the n-side. This reverse current is called the *Zener effect*.

These three modes of reverse voltage breakdown are not necessarily destructive provided the current is uniformly distributed and limited by the external circuit. If the current density in a particular area is too high, a local hot spot may occur, leading to device thermal destruction.

# 2.3 Thermal effects

The pn junction current, I, shown in figure 2.2, is related to the scl voltage, v, according to

$$I(v) = I_o[e^{-qv/kT_j} - 1]$$

(A)

where  $I_0$  is the reverse (saturation) leakage current in amps and is defined in figure 2.5.

The forward conduction voltage decreases with increased junction temperature,  $T_j$ . That is, the on-state voltage has a negative temperature coefficient. In practical silicon pn diodes, at low currents, the temperature coefficient is typically -2.4 mV/K, becoming less negative with increased current. At higher currents, the coefficient becomes positive because of the reduced carrier mobility at higher temperatures, which causes non-scl regions to increase in resistance. The effects of the change in temperature coefficient at higher currents, in practical devices, are shown dotted in figure 2.2. Neglecting the exponential silicon band gap temperature dependence, the temperature effects at high current, on the diffusion constant component of the leakage current  $I_0$  in equation (2.6), called the saturation current, is given by

$$I_o(T) = I_o(25^{\circ}\text{C}) \times \left(\frac{T}{300}\right)^{1.8}$$

(2.7)

Silicon carbide diodes have a higher temperature coefficient, typically +8mV/K.

The avalanche voltage increases with temperature, as does the reverse leakage current. The effects of temperature on the reverse bias characteristics are shown in figure 2.2. In the case of silicon carbide, increased temperature decreases the avalanche voltage and increases the leakage current.

The silicon temperature coefficient for avalanche is positive since the mean distance between collisions is reduced due to the increased thermal energy, which increases the vibrational amplitude. Higher electric fields are necessary for the carriers to gain sufficient kinetic energy for ionisation.

Equation (2.6) also indicates that the reverse bias current increases with increased junction temperature. This positive temperature coefficient does not generally result in thermal instability with silicon devices, provided sufficient heat sinking is employed on smaller devices.

# Example 2.2: Diode forward bias characteristics

A pn junction diode has a reverse saturation current of 100nA at a junction operating temperature of 28°C. What is the forward current when the forward bias voltage is 0.5V and the dynamic ac resistance at that current?

#### Solution

The diode current is given by equation (2.6), namely

$$I(v) = I_o[e^{-qv/kT_j} - 1]$$

(A)

where  $V_T = q/kT_j = 0.0259V$  at 300K, 28°C.

$I(0.5V) = 100 \times 10^{-9} \times [e^{v/0.0259} - 1]$

= 26.1A

Differentiating the diode I-V equation with respect to voltage gives

$$\frac{di}{dv} = \frac{I_o}{V_T} e^{\frac{V_F}{V_T}} = \frac{1}{R_{ac}}$$

$$= \frac{100 \times 10^{-9} \text{A}}{0.0258 \text{V}} \times e^{\frac{0.5 \text{V}}{0.0258 \text{V}}}$$

$$\Rightarrow R_{ac} = 1.0 \text{m}\Omega$$

#### 2.4 Models for the bipolar junction diode

Semiconductor device electrical models are used extensively for power electronic circuit simulation. A basic piecewise-linear model is applicable to simple manual calculations, where the terminal I-V characteristics are empirically modelled based on ideal circuit elements. A more complex and accurate model is required for computer transient circuit analysis simulation. Such accurate models are based on the semiconductor physics of the device. Many power switching semiconductor device manufacturers provide values for the model parameters suitable for circuit simulation in the packages PSpice and SABER.

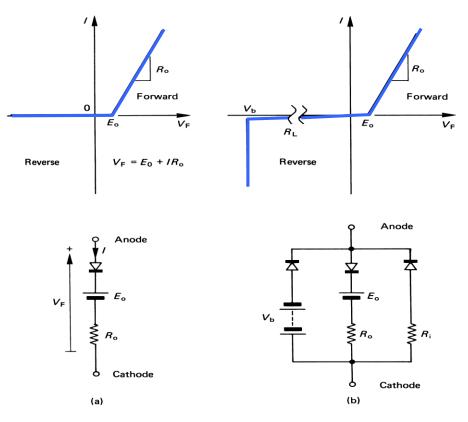

#### 2.4.1 Piecewise-linear junction diode model

The pn junction diode is a unilateral device that, to a good approximation, conducts current in only one direction. Figure 2.4a shows a *piecewise-linear* (pwl) model of the diode that is suitable for static modelling in power electronic circuits. It includes a perfect diode, an on-state voltage source  $E_o$ , and a series resistor of resistance value  $R_o$  to account for the slope in the actual forward conduction characteristic. The forward I-V characteristic at a given temperature is given by

$$V_{F}(I_{F}) = E_{0} + I_{F}R_{0} \quad \text{for } V_{F} > E_{0}$$

(V)

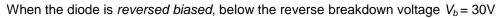

The model in figure 2.4a does not incorporate the static reverse characteristics of leakage and avalanche. These are shown in figure 2.4b, where  $V_b$  from equation (2.3) models the avalanche limit and  $R_i \left(=V_b / I_o\right)$  gives linear leakage current properties for a given junction temperature. The three diode components in figure 2.4b are assumed ideal.

The model given by equation (2.8) is adequate for calculation of static balancing requirements of parallel and series connected diodes and thyristors, as considered in section 11.1 and the associated problems, 11.4, 11.5, and 11.9 to 11.12.

Figure 2.4. Piecewise-linear approximations of junction diode characteristics:

(a) ideal diode with an offset voltage and resistance to account for slope in the forward characteristic and (b) model including reverse bias characteristics.

# Example 2.3: Using the pwl junction diode model

An approximation to the forward I-V characteristic of the diode shown in figure 2.4a, is given by  $V_F(I_F) = 1.0 + 0.01 I_F$ . For a constant current of 45A for  $\frac{2}{3}$  of a cycle, calculate the diode

- i. on-state voltage;

- ii. mean power loss; and

- iii. rms current.

#### Solution

i. The on-state voltage at 45A is given by

$$V_F$$

(45A) = 1.0 +  $I_F$  0.01 = 1.0V + 45A × 0.01 $\Omega$  = 1.45V

ii. If the on-state duty cycle is  $\delta = \frac{2}{3}$ , the average power loss is

$$P = \delta \times V_F \times I_F = \frac{2}{3} \times 1.45 \text{V} \times 45 \text{A} = 43.2 \text{W}$$

iii. The diode rms current is given by

$$I_{ms} = \sqrt{\delta} \times I_{dc} = \sqrt{\frac{2}{3}} \times 45A = 36.7A$$

#### Example 2.4: Static linear diode model

A Schottky diode is used to half-wave rectify a square wave  $\pm 15V$  source in series with a  $1\Omega$  load resistor. If the diode model shown in figure 2.4b is modelled with  $R_o = 0.01~\Omega$ ,  $E_o = 0.2V$ ,  $R_i = 1000\Omega$ , and  $V_b = 30V$ , determine:

- i. the diode model forward and reverse bias operating point equations for the series circuit

- ii. the load current and diode voltage

- iii. the rectifier losses (neglecting any recovery effects) and the load power dissipation

- *iv.* estimate the power dissipated in the load if the source is ac with the same fundamental component as the square wave

- v. what is the non-fundamental power dissipated with the square wave source?

#### Solution

i. When the diode is forward biased

$$i_F = \frac{1}{R_o} (V_{DF} - E_o)$$

for  $V_{DF} \ge 0.2V$

Kirchhoff's voltage law for the series circuit gives

$$V_s = I_F R_L + V_{DF}$$

Eliminating the diode voltage  $v_{DF}$  gives the series circuit current

$$i_F = \frac{V_s - E_o}{R_o + R_L}$$

for  $V_s \ge E_o$

$i_F = 0$  for  $0 < V_s < E_o$

The diode forward voltage is therefore given by

$$V_{DF} = \frac{V_s R_o + E_o R_L}{R_o + R_L} = E_o + i_F R_o \text{ for } i > 0$$

$$i_R = \frac{1}{R_j} V_{DR}$$

for  $V_{DR} < V_b$

$V_s = i_R R_L + V_{DR}$

Eliminating the diode voltage  $v_{DR}$  gives the series circuit leakage current

$$i_R = \frac{V_s}{R_i + R_i}$$

The diode reverse voltage is thus given by

$$V_{DR} = \frac{V_s R_i}{R_i + R_i} = I_R R_i$$

ii. The circuit voltages and current are, when the diode is forward biased,

$$i_F = \frac{15V - 0.2V}{0.01\Omega + 1\Omega} = 14.65A$$

$V_{D_F} = 0.2V + 14.65A \times 0.01\Omega = 0.35V$

If  $R_L >> R_o$ , the diode forward current equation can be simplified using  $R_o = 0$ . When the diode is reverse biased

$$i_R = \frac{15V}{1000\Omega + 1\Omega} = 15.0 \text{mA}$$

$V_{D_R} = 15 \text{mA} \times 1000\Omega = 15.0 \text{V}$

If  $R_i >> R_L$  the diode reverse current and voltage equations can be simplified using  $R_L = 0$ .

iii. The rectifier losses are, when forward biased

$$P_{d_F} = V_{D_F} \times I_F$$

= 0.35V × 14.65A = 5.127W

and when reverse biased

$$P_{d_R} = V_{D_R} \times I_R$$

= 15V × 15mA = 0.225W

Total diode losses for a square wave are therefore  $\frac{1}{2}$ x(5.127W + 0.225W) = 2.68W.

The power from the square wave supply is

$$\frac{1}{2} \times (15 \text{V} \times 14.65 \text{A} + 15 \text{V} \times 15 \text{mA}) = 110.0 \text{ W}$$

with 110W - 2.68W = 107.32W dissipated in the  $1\Omega$  load resistor.

iv. The magnitude of the fundamental of a square wave is  $4/\pi$  times the square wave magnitude, that is,  $15V \times 4/\pi = 19.1V$  peak.

The forward biased diode does not conduct until the supply voltage exceeds 0.2V. This is a small percentage of the sine wave magnitude ( $\approx$ 1%), hence can be neglected in the loss estimate. The forward current flow is approximately

$$i_F = \frac{19.1 \text{V} - 0.2 \text{V}}{1\Omega + 0.01\Omega} \times \sin \omega t = 18.7 \times \sin \omega t$$

The rms of a sine is  $1/\sqrt{2}$  its magnitude and  $1/\sqrt{2}$  again for a half-wave rectified sine. That is

$$i_{Fms} = \frac{18.7A}{\sqrt{2}\sqrt{2}} = 9.35A \text{ rms}$$

The reverse leakage current is given by

$$i_{R} = \frac{19.1V}{1000\Omega + 1\Omega} \times \sin \omega t = 0.019 \times \sin \omega t$$

which gives an rms current of

$$i_{Rrms} = \frac{19\text{mA}}{\sqrt{2}\sqrt{2}} = 9.5\text{mA rms}$$

The power dissipated in the  $1\Omega$  load resistor is

$$P_{L} = (i_{F_{ms}}^{2} + i_{R_{ms}}^{2}) \times R_{L}$$

$$= (9.35^{2} + 0.0095^{2}) \times 1\Omega = 87.42W + 90\mu W = 87.42W$$

Clearly, if  $R_L \ll R_i$ , the reverse leakage current related power component is negligible.

*v.* With the square wave, from part iii., 107.32W are dissipated in the load but from part iv., only 87.42W are dissipated for a sine wave with the same fundamental magnitude. The 19.9W difference is power produced by the harmonics of the fundamental (3<sup>rd</sup>, 5<sup>th</sup>, ...). For a resistive heating load this power produces useful heating, but in a motor the harmonic power would produce unwanted torque pulsations and motor heating.

# \*

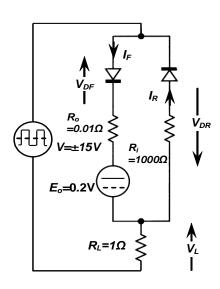

# 2.4.2 Semiconductor physics based junction diode model

The charge-carrier diode model shown in figure 2.5 is necessary for transient (time domain) circuit analysis involving diodes. The pn junction diode is assumed to have an abrupt or step junction. The model components are voltage dependant current sources, I and  $I_b$ , voltage dependant capacitances  $C_t$  and  $C_b$ , and series access resistance  $R_s$ .

Figure 2.5. PSpice transient analysis circuit model of the pn junction diode.

The ideal diode current I is given by equation (2.6). The diode current  $I_b$  models reverse voltage breakdown, where the breakdown voltage  $V_b$  is assumed due to avalanche and is given by equation (2.3). The voltage dependant transit capacitance,  $C_t$ , which is dominant under forward bias, is related to the minority carrier lifetime  $t_t$ . The voltage dependant scl (depletion layer) capacitance  $C_j$ , which is dominant under reverse bias, involves the zero bias junction potential voltage  $\Phi$ , given by equation (2.1) and the zero bias junction capacitance  $C_{jo}$ . In the case of the silicon carbide Schottky diode,  $C_j >> C_t$ . The scl capacitance,  $C_j(V)$  can be evaluated from the pn diode structure and doping profile, as follows.

#### 2.4.2i - Determination of zero bias junction capacitance, Cio

Poisson's equation, in conjunction with Gauss's law, for the one dimensional step junction shown in figure 2.6, give the scl electric field,  $\xi$ , and potential voltage, V:

$$\frac{d^2V}{dx^2} = -\frac{d\xi}{dx} = \frac{qN_D}{\varepsilon_S} = -\frac{qN_A}{\varepsilon_S}$$

(2.9)

Figure 2.6. The charge Q, electric field  $\xi$ , and voltage potential V, in the space charge layer of a step pn junction.

The dielectric permittivity  $\varepsilon_s = \varepsilon_r \varepsilon_o$  comprises the free space permittivity  $\varepsilon_o = 8.854 \text{x} 10^{-12}$  F/m and the relative permittivity  $\varepsilon_r = 11.8$  for silicon and 9.7 for SiC.

$$\frac{d\xi(x)}{dx} = \begin{cases}

\frac{q}{\varepsilon_s} N_D & \text{for } -x_n < x < 0 \\

-\frac{q}{\varepsilon_s} N_A & \text{for } 0 < x < x_p

\end{cases}$$

(2.10)

Integrating both parts of equation (2.10) over the shown bounds, gives  $\xi(x)$ :

$$\frac{dV(x)}{dx} = \xi(x) = \begin{cases}

\frac{q}{\varepsilon_s} N_D x + \xi_m & \text{for } -x_n < x < 0 \\

-\frac{q}{\varepsilon_s} N_A x + \xi_m & \text{for } 0 < x < x_p

\end{cases}$$

(2.11)

where the maximium field intensity (at x = 0) is  $\xi_m = \frac{q}{\varepsilon_s} N_D X_n = \frac{q}{\varepsilon_s} N_A X_\rho$

The piece-wise parabolic voltage potential across the scl shown in figure 2.6, is given by integration of the electric field, that is

$$V = \int_{-x_n}^0 \left(\frac{q}{\varepsilon_s} N_D X + \xi_m\right) dX + \int_0^{x_p} \left(-\frac{q}{\varepsilon_s} N_A X + \xi_m\right) dX$$

$$= \frac{1}{2} \xi_m W_0$$

(2.12)

Since the charges each side of the metallurgical junction must balance, equation (2.12) can be rearranged to give the scl width.

$$W_o = \sqrt{\left[\frac{2\,\varepsilon_s V}{q} \left(\frac{1}{N_A} + \frac{1}{N_D}\right)\right]} \tag{2.13}$$

From equation (2.1), a zero bias voltage  $\Phi$  exists without the presence of any external voltage. Therefore, to incorporate non-equilibrium conditions, the electrostatic barrier potential becomes  $\Phi$ -V, where V is the externally applied reverse bias voltage. Consequently the scl width expression becomes:

$$W_{scl} = \sqrt{\left[\frac{2\varepsilon_s \left(\boldsymbol{\Phi} - V\right)}{q} \left(\frac{1}{N_A} + \frac{1}{N_D}\right)\right]}$$

(2.14)

The scl width voltage dependence can be expressed in terms of the zero bias scl width,  $W_o$

$$W_{scl}(V) = \sqrt{\left[\frac{2\varepsilon_{s} \Phi}{q} \left(\frac{1}{N_{A}} + \frac{1}{N_{D}}\right)\right]} \sqrt{I - \frac{V}{\Phi}}$$

$$= W_{0} \sqrt{I - \frac{V}{\Phi}}$$

(2.15)

$$X_{n0} = \frac{W_{0}}{1 + N_{D} / N_{A}} \qquad X_{p0} = \frac{W_{0}}{1 + N_{A} / N_{D}}$$

$$X_{n}(V) = X_{n0} \sqrt{I \cdot \frac{V}{\Phi}} \qquad X_{p}(V) = X_{p0} \sqrt{I \cdot \frac{V}{\Phi}}$$

(2.16)

The magnitude of the voltage dependant charge on each side of the junction is

$$|Q(V)| = q A \frac{N_D N_A}{N_D + N_A} W = A \left[ 2q \varepsilon_s \Phi \frac{N_D N_A}{N_D + N_A} \right]^{\frac{1}{2}} \sqrt{I - \frac{V}{\Phi}}$$

$$= Q_0 \sqrt{I - \frac{V}{\Phi}}$$

(2.17)

The junction capacitance is given by differentiation of equation (2.17) with respect to V

$$C_{j} = \left| \frac{dQ}{dV} \right| = \varepsilon_{s} A \left[ \frac{Q}{2\varepsilon_{s}(\boldsymbol{\Phi} - \boldsymbol{V})} \frac{N_{D} N_{A}}{N_{D} + N_{A}} \right]^{\frac{1}{2}} = \frac{\varepsilon_{s} A}{W}$$

(2.18)

Equation (2.18) can be rearranged to give the PSpice capacitance form, in terms of the zero bias junction capacitance  $C_{io}$ .

$$C_{j}(V) = \frac{C_{jo}}{\left(1 - \frac{V}{\Phi}\right)^{\frac{1}{2}}}$$

where  $C_{jo} = \varepsilon_{s} A \left[\frac{q}{2\varepsilon_{s} \Phi} \frac{N_{D} N_{A}}{N_{D} + N_{A}}\right]^{\frac{1}{2}} = \frac{\varepsilon_{s} A}{W_{o}}$  (2.19)

The electric field at the metallurgical junction, from equation (2.12) is given by

$$\xi_j(V) = \xi_0 \sqrt{I - \frac{V}{\Phi}}$$

where  $\xi_0 = 2\Phi / W_0$  (2.20)

#### 2.4.2ii - One-sided pn diode equations

When  $N_A >> N_D$ , which is the usual case in high voltage pn diodes, equations (2.12) to (2.20) are approximated by the following one-sided diode equations.

$$W_{0} = \sqrt{\left[\frac{2\varepsilon_{s} \, \Phi}{q \, N_{D}}\right]} \approx X_{no} \quad \text{and} \quad X_{po} \approx 0$$

$$Q_{0} = A\sqrt{2q\varepsilon_{s}\Phi N_{D}}$$

$$C_{jo} = \varepsilon_{s} A\sqrt{\frac{qN_{D}}{2\varepsilon_{s}\Phi}} = \frac{\varepsilon_{s} A}{W_{o}}$$

$$(2.21)$$

These equations show that the scl penetrates mostly into the n-side, (hence the name one-sided), which supports most of the voltage, as shown in the last diagram in figure 2.6.

# Example 2.5: Space charge layer parameter values

A 10 $\mu$ m thick p-type  $2x10^{16}$  /cc silicon epitaxial layer is grown on an n<sup>-</sup> - type  $1x10^{14}$  /cc silicon substrate, of area 1 cm<sup>2</sup>, to form an abrupt pn junction.

Calculate the following PSpice parameter values, at room temperature:

- *i.* zero bias junction potential,  $\phi$ ;

- ii. zero bias scl width, maximum electric field, charge, and junction capacitance,

$W_0$ ,  $\xi_0$ ,  $Q_o$ ,  $C_{io}$ ; and

iii. avalanche breakdown voltage,  $V_b$ .

If the substrate is 150µm thick, for a 1000V reverse bias, calculate:

- iv. scl width and penetration depth each side of the junction, W,  $x_n$ ,  $x_p$ ;

- v. charge each side of the junction, maximum electric field, and the capacitance, Q,  $\xi_h$   $C_h$

#### Solution

i. From equation (2.1), the zero bias built-in voltage is

$$\Phi = \frac{kT_j}{q} \ell n \frac{N_A N_D}{n_i^2} = 0.0259 \ell n \frac{2 \times 10^{16} \times 1 \times 10^{14}}{2.25 \times 10^{20}}$$

$$= 0.0259 \times \ell n (8.89 \times 10^9) = 0.534V$$

ii. From equations (2.15), (2.20), (2.17), and (2.19)

$$W_{0} = \sqrt{\left[\frac{2\Phi \,\varepsilon_{s}}{q} \times \left(\frac{1}{N_{A}} + \frac{1}{N_{D}}\right)\right]}$$

$$W_{0} = \sqrt{\left[\frac{2 \times 0.53 \, \text{V} \times 11.8 \times 8.85 \times 10^{-12}}{1.6 \times 10^{-19}} \times \left\{\frac{1}{2 \times 10^{22}} + \frac{1}{1 \times 10^{20}}\right]} = 2.65 \, \mu\text{m}$$

$$\varepsilon_{0} = 2 \, \Phi / W = 2 \times 0.534 / 2.65 \, \mu\text{m}$$

$$\xi_0 = 2 \, \Phi \, / \, W = 2 \times 0.534 \, / \, 2.65 \mu \mathrm{m}$$

$\xi_0 = 0.40 \, \mathrm{MV/m}$

$$Q_o = A \left[ 2\Phi q \, \varepsilon_s \, \frac{N_D \, N_A}{N_D + N_A} \right]^{\frac{1}{2}}$$

$$Q_o = 1 \times 10^{-4} \sqrt{2 \times 0.53 \, \text{V} \times 1.6 \times 10^{-19} \times 11.8 \times 8.85 \times 10^{-12} \times \frac{2 \times 10^{42}}{2.01 \times 10^{22}}} = 4.21 \, \text{nC}$$

$$C_{jo} = A \left[ \frac{q \varepsilon_s}{2 \Phi} \frac{N_D N_A}{N_D + N_A} \right]^{\frac{1}{2}}$$

$$C_{jo} = 1 \times 10^{-4} \times \left[ \frac{1.6 \times 10^{-19} \times 11.8 \times 8.85 \times 10^{-12}}{2 \times 0.53 \text{V}} \times \frac{2 \times 10^{42}}{2.01 \times 10^{22}} \right]^{\frac{1}{2}}$$

$$= 3.95 \times 10^{-9} \text{F} = 3.95 \text{ nF}$$

iii. From equation (2.2), the estimated punch-through voltage is

$$V_{\rho_T} = 7.67 \times 10^{-16} N_c W_c^2 = 7.67 \times 10^{-16} \times 10^{14} \times (150)^2$$

= 1727V

That is, punch through occurs when the reverse bias is greater than the operating voltage, 1000V. If the diode is to breakdown due to avalanche then the avalanche breakdown voltage given by  $V_b$  (equation (2.3)) must be less than  $V_{PT}$ , 1727V.

$$V_b = 5.34 \times 10^{13} \ N_c^{-3/4} = 5.34 \times 10^{13} \times (1 \times 10^{14})^{-3/4}$$

= 1689V

iv. From equation (2.15) the scl width at -1000V reverse bias is

$$W_{scl} = W_0 \sqrt{l - \frac{V}{\Phi}} = 2.65 \mu \sqrt{1 + \frac{1000V}{0.533V}}$$

= 114.6 \mu m

From equation (2.16) the scl penetration into each side of the junction at -1000V is

$$X_{n} = \frac{W_{scl}}{1 + N_{D} / N_{A}} = \frac{114.6}{1 + 0.005}$$

$X_{p} = \frac{W_{scl}}{1 + N_{A} / N_{D}} = \frac{114.6}{1 + 200}$   $X_{p} = 114.0 \mu m$   $X_{p} = 0.57 \mu m$

Note that when  $N_A >> N_D$ ,  $x_n \approx W_{scl}$ , thus the lower the relative concentration of  $N_D$ , the deeper the scl penetration and the higher the portion of V supported in  $N_D$ . The junction scl can under these circumstances be analysed based on simplified equations – called one-sided junction equations.

v. The charge magnitude each side of the junction, shown in figure 2.6, is given by equation (2.17). The electric field at the junction is given by equation (2.20), while the junction capacitance at -1000V is given by equation (2.19):

$$Q_{j} = Q_{0}\sqrt{I \cdot \frac{V}{\Phi}} = 4.2\text{nC} \times \sqrt{1 + \frac{1000\text{V}}{0.533\text{V}}}$$

$$= 182 \cdot 4\text{nC}$$

$$\xi_{j} = \xi_{0}\sqrt{I \cdot \frac{V}{\Phi}} = 0.40\text{M} \times \sqrt{1 + \frac{1000\text{V}}{0.533\text{V}}}$$

$$\xi_{j} = 17.5\text{MV/m} \qquad \left( < \xi_{b} = 25\text{MV/m} \right)$$

$$C_{j} = C_{jo} \left( I \cdot \frac{V}{\Phi} \right)^{\frac{1}{2}} = 3.95\text{n} \times \left( 1 + \frac{1000\text{V}}{0.533\text{V}} \right)^{\frac{1}{2}}$$

$$C_{j} = 91\text{pF}$$

$$C_{j} = 91\text{pF}$$

$$C_{jo} = \frac{3.95\text{nF}}{\left( 1 \cdot \frac{V}{0.533} \right)^{\frac{1}{2}}}$$

$$C_{jo} = \frac{3.95\text{nF}}{0.534\text{V}}$$

# **Reading list**

See chapter 1 reading list.

Fraser, D. A., *The Physics of Semiconductor Devices*, OUP, 1977.

Wolf, H. F., Semiconductors,

John Wiley-Interscience, New York, 1977.

Van Zeghbroeck, B., Principles of Semiconductor Devices,

//ece-www.colorado.edu/~bart/book, 2004.

Yang, E. S., Fundamentals of Semiconductor Devices,

McGraw-Hill, 1978.

#### **Problems**

- 2.1. A silicon diode is to have a breakdown voltage of 1000 V. If breakdown is due to the avalanche mechanism calculate

- i. the concentration of the n region

- ii. the width of the n region

- iii. the maximum electric field

- iv. the expected punch-through voltage based on parts i. and ii.

$[2 \times 10^{14}/\text{cc}, 83\mu\text{m}, 2.4\times 10^{5} \text{ V/cm}, 1057 \text{ V}]$

2.2. What is the punch-through voltage for a silicon step junction with an n doping level of 5x10<sup>13</sup> /cc and a width of 20µm? Calculate the doping level and scl width for a similarly voltage rated silicon avalanche diode assuming equations (2.3) and (2.5) are valid.

[15.3 V, 5.27x10<sup>16</sup>/cc, 0.63µm]

- 2.3. An abrupt silicon pn junction consists of a p-type region containing 10<sup>16</sup> cm<sup>-3</sup> acceptors and an n-type region containing 5x10<sup>14</sup> cm<sup>-3</sup> donors. Calculate the built-in potential of this p-n junction. When the applied voltage equals 0, 0.5V, and -100V calculate:

- i. the total width of the scl region.

- ii. maximum electric field in the scl region.

- iii. the potential across the scl region in the n-type semiconductor.

- 2.4. Consider an abrupt pn diode with  $N_A = 10^{18}$  cm<sup>-3</sup> and  $N_D = 10^{16}$  cm<sup>-3</sup>. Calculate the junction capacitance at zero bias if the diode area is  $10^{-4}$  cm<sup>2</sup>. Repeat the problem while treating the diode as a one-sided diode and calculate the relative error.

- 2.5. Repeat example 2.2 using the single-sided diode equations in equation (2.21), where  $N_A >> N_D$ . Calculate the percentage error in using the assumptions.

- 2.6. A silicon pn diode with  $N_A = 10^{18}$  cm<sup>-3</sup> has a capacitance of  $10^{-7}$  F/cm<sup>2</sup> at an applied reverse voltage of 1V. Calculate the donor density  $N_D$ .

- 2.7. A silicon pn diode has a maximum electric field magnitude of 10<sup>7</sup> V/cm and a scl width of 200μm. The acceptor concentration is 100 times the donor density. Calculate each doping density.

- 2.8. Repeat example 2.2 for the equivalent 4H silicon carbide junction diode having the same electrical operating conditions. Use the silicon carbide data given below.

See problems 11.4, 11.5, and 11.9 to 11.12.

Useful SI data for silicon and silicon carbide:

$$q = -1.6 \times 10^{-19} \text{ C}$$

$\xi_o = 8.85 \times 10^{-12} \text{ F/m}$   $\xi_{r, \text{Si}} = 11.8$   $\xi_{r, \text{SiC}} = 9.7$   $kT/q = 0.0259 \text{ eV}$  at 300K  $n_{i, \text{Si}} = 1.5 \times 10^{16} \text{ m}^{-3}$   $n_{i, \text{SiC}} = 2.5 \times 10^{-3} \text{ m}^{-3}$

Blank