# **C**HAPTER

# Basic Semiconductor Physics and Technology

Power electronic circuits utilise power semiconductor switching devices which *ideally* present infinite resistance when off, zero resistance when on, and switch instantaneously between those two states. It is necessary for the power electronics engineer to have a general appreciation of the semiconductor physics aspects applicable to power switching devices so as to be able to understand the vocabulary and the non-ideal device electrical phenomena. To this end, it is only necessary to attempt a qualitative description of switching devices and the relation between their geometry, material parameters, and physical operating mechanisms.

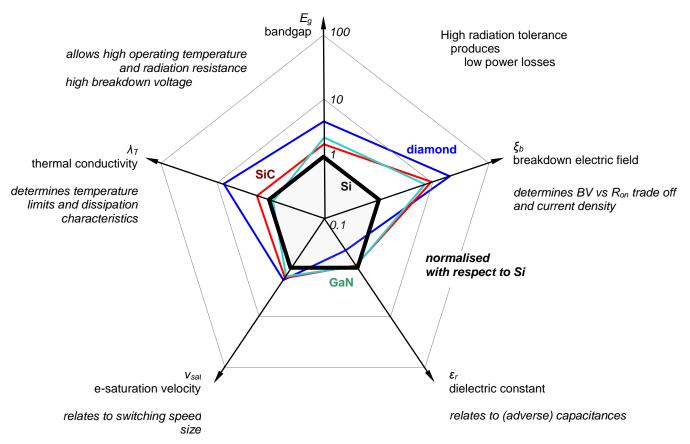

Typical power switching devices such as diodes, thyristors, and transistors are based on a monocrystalline group IV silicon semiconductor structure or, increasingly, a group IV polytype, silicon carbide. These semiconductor materials are distinguished by having a specific electrical conductivity,  $\sigma$ , somewhere between that of good conductors (>10<sup>20</sup> free electron density) and that of good insulators (<10<sup>3</sup> free electron density). Silicon is less expensive, more widely used, and a more versatile processing material than silicon carbide, thus the electrical characteristics and processing properties of silicon are considered first, and in more detail.

In pure silicon at equilibrium, the number of *electrons* is equal to the number of *holes*. The silicon is called *intrinsic* and the electrons are considered as negative charge-carriers. Holes and electrons both contribute to conduction, although holes have less mobility due to the covalent bonding. Electron-hole pairs are continually being *generated* by thermal ionization and in order to preserve equilibrium previously generated pairs *recombine*. The intrinsic carrier concentrations  $n_i$  are equal, small  $(1.4 \times 10^{10}/\text{cc})$ , and highly dependent on temperature. In order to fabricate a power-switching device, it is necessary to increase greatly the free hole or electron population. This is achieved by deliberately doping the silicon, by adding specific impurities called *dopants*. The doped silicon is subsequently called *extrinsic* and as the concentration of dopant  $N_c$  increases, the resistivity  $\rho = 1/\sigma$  decreases.

- *n-type*:- Silicon doped with group V elements, such as As, Sb or P, will be rich in electrons compared to holes. Four of the five valence electrons of the group V dopant will take part in the covalent bonding with the neighbouring silicon atoms, while the fifth electron is only weakly attached and is relatively 'free'. The semi-conductor is called *n-type* because of its free negative charge-carriers. A group V dopant is called a *donor*, having donated an electron for conduction. The resultant electron impurity concentration is denoted by N<sub>D</sub> the donor concentration.

- *p-type*:- If silicon is doped with atoms from group III, such as B, A*l*, Ga or In, which have three valence electrons, the covalent bonds in the silicon involving the dopant will have one covalent-bonded electron missing. The impurity atom can accept an electron because of the available thermal energy. The dopant is thus called an *acceptor*, which is ionised with a net positive charge. Silicon doped with acceptors is rich in holes and is therefore called *p-type*. The resultant hole impurity concentration is denoted by *N*<sub>A</sub> the acceptor concentration.

Electrons in n-type silicon and holes in p-type are called *majority carriers*, while holes in n-type and electrons in p-type are called *minority carriers*. In a given silicon material, at equilibrium, the product of the majority and minority carrier concentration is a constant:

$$p_o \times n_o = n_i^2 \tag{1.1}$$

where  $p_o$  and  $n_o$  are the hole and electron equilibrium carrier concentrations.

Therefore, the majority and minority concentrations are given by:

for an *n*-type

$$n_o = N_D$$

therefore  $p_o = \frac{n_i^2}{N_D}$  and

for a *p*-type  $p_o = N_A$  therefore  $n_o = \frac{n_i^2}{N_A}$  (1.2)

These equations show that the number of minority carriers decreases as the doping level increases. The resistivity,  $\rho$ , of doped silicon is

$$\rho = \frac{1}{\sigma} = \frac{1}{q\left(\mu_n n + \mu_p p\right)} = \frac{E}{J} = \frac{V}{L} / \frac{I}{A}$$

(1.3)

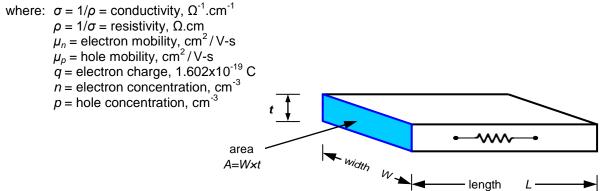

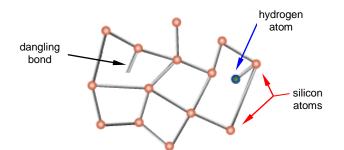

Figure 1.1. Elemental doped silicon.

Resistance of semiconductor materials is usually expressed in terms of sheet resistance  $R_{\Box}$ , which is related to resistance as follows. At a given temperature, the impurity depth  $x_{j}$ , mobility  $\mu$ , and impurity distribution N(x) are related to sheet resistance by

$$R_{\Box} = \frac{1}{q \int_{a}^{x_{j}} \mu N(x) dx} \qquad \text{(1.4)}$$

The average resistivity is  $\overline{\rho} = R_{a}x_{j}$  and given a length *L* and width *w*, as defined in figure 1.1, the resistance, *R*, is given by

For parallel n-doped profiles, the resistance can be estimated by treating each layer independently:

$$R_{tota'}^{-1} = R_1^{-1} + R_2^{-1} + \dots = \frac{wt_1}{L\rho_1} + \frac{wt_1}{L\rho_1} + \dots = \frac{w}{L} \left( \frac{t_1}{\rho_1} + \frac{t_1}{\rho_1} + \dots \right) = \frac{w}{L} \left( R_{D1}^{-1} + R_{D2}^{-1} + \dots \right) = \sum_{i=1}^{N} q \,\mu_{ni} N_{Di} t_i$$

(1.6)

#### Example 1.1: Resistance of homogeneously doped silicon

Silicon doped with phosphorous ( $N_D = 10^{17}$ /cm<sup>3</sup>) measures 100µm by 10µm by 1µm. Calculate the sheet resistance and resistance between opposite faces, assuming the electron mobility at this doping level is  $\mu_n = 720$ cm<sup>2</sup>/V-s. Doping to produce a p-type material has a hole mobility of 40% that for electrons. Recalculate sheet resistance and resistance values.

#### Solution

From equation (1.3), the resistivity,  $\rho$ , of doped silicon is

$$\rho = \frac{1}{\sigma} = \frac{1}{q(\mu_n n + \mu_p p)}$$

Since n >> p in the n-type silicon and assuming complete ionization

$$\rho \approx \frac{1}{q\mu_n n} \approx \frac{1}{q\mu_n N_D} = \frac{1}{1.6 \times 10^{-19} \times 720 \times 10^{17}} = 0.086 \,\Omega \text{cm}$$

For a length of 100µm, the resistance is

$$R = \rho \times \frac{Length}{Area} = \rho \times \frac{L}{W \times t} = 0.086 \times \frac{100 \times 10^{-4}}{10 \times 10^{-4} \times 1 \times 10^{-4}} = 8.6 \,\mathrm{k\Omega}$$

From equation (1.5) the sheet resistance is given by

$$R_s = R \frac{W}{L} = 8.6 \,\mathrm{k}\Omega \times \frac{10 \times 10^{-4}}{100 \times 10^{-4}} = 860 \,\Omega/\mathrm{square}$$

If the length is assumed to be one of the shorter dimensions, then for a length 10µm or 1µm, the resistance is 86 $\Omega$  or 0.86 $\Omega$ , respectively, while the sheet resistance possibilities, depending on the thickness reference axis, are 86  $\Omega$ /square and 8.6  $\Omega$ /square.

For a p-type material, the 40% decrease in mobility of holes  $\mu_p$  increases resistivity by a factor of 1/0.4 = 2.5. Each aspect resistance therefore increases by a factor 2.5, viz., increases to 21.5k $\Omega$ , 215 $\Omega$ , and 2.15 $\Omega$  for lengths 100 $\mu$ m, 10 $\mu$ m, and 1 $\mu$ m, respectively. From equation (1.4) the sheet resistances are increased to 2.15k $\Omega$ /square, 215 $\Omega$ /square, and 21.5 $\Omega$ /square.

#### \*

The carrier concentration equilibrium can be significantly changed by irradiation with photons, the application of an electric field or by heat. Such carrier injection mechanisms create *excess carriers*.

If n-type silicon is irradiated by photons with enough energy to ionise the valence electrons, electron-hole pairs are generated. There is already an abundance of majority electrons in the n-type silicon, thus the photon-generated excess minority holes are of more relative and detectable importance. If the light source is removed, the time constant associated with recombination, or decay of excess minority carriers, is called the *minority carrier hole lifetime*,  $\tau_h$ . For a p-type silicon, exposed to light, excess minority electrons are generated and after the source is removed, decay at a rate called the *minority carrier electron lifetime*,  $\tau_e$ . The minority carrier lifetime is often termed the *recombination lifetime*.

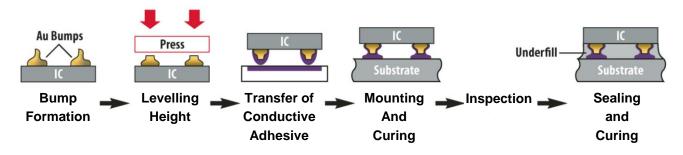

A manufacturing processing difficulty with high-voltage, large-area semiconductor devices is that of obtaining uniformity of n-type phosphorus doping throughout the usual high-resistivity silicon starting material. Normal crystal growing (by liquid encapsulated, contactless, Czochralski crystal growth – see section 1.19.3i) and doping techniques give no better than  $\pm 10$  per cent fluctuation around the wanted resistivity at the required low concentration levels (<10<sup>14</sup>/cc). Final device electrical properties will therefore vary widely in all lattice directions. Tolerances better than  $\pm 1$  per cent in resistivity and homogeneous

distribution of phosphorus can be attained by neutron radiation, commonly called *neutron transmutation doping*, NTD. The neutron irradiation flux transmutes silicon atoms first into a silicon isotope with a short 2.62-hour half-lifetime, which then decays into phosphorus. Subsequent thermal annealing removes any crystal damage caused by the irradiation. Neutrons can penetrate over 100mm into silicon, thus large silicon crystals can be processed using the NTD technique.

A p-n junction is the location in a semiconductor where the doping changes from p to n while the monocrystalline lattice continues undisturbed. A bipolar diode is thus created, which forms the basis of any bipolar semiconductor device.

The donor-acceptor doping junction is formed by any one of a number of process techniques, namely alloying, diffusion, epitaxy, ion implantation or the metallization for ohmic contacts.

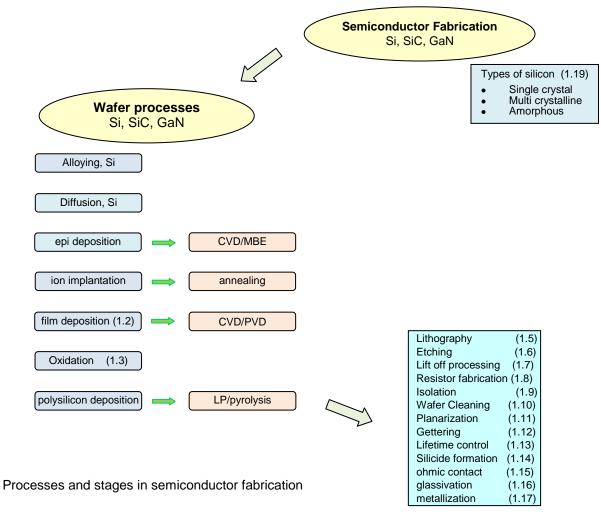

Power semiconductor device processing involves most of the following range of process possibilities.

- **Deposition** is any process that grows, coats or otherwise transfers a material onto the wafer. Available technologies consist of physical vapour deposition (PVD), chemical vapour deposition (CVD), electrochemical deposition, molecular beam epitaxy (MBE), and atomic layer deposition.

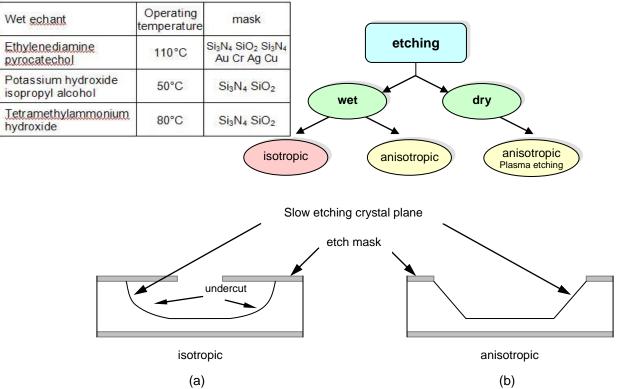

- **Removal** processes are any that remove material from the wafer either in bulk or selective form and consist primarily of etch processes, both wet etching and dry etching such as reactive ion etch.

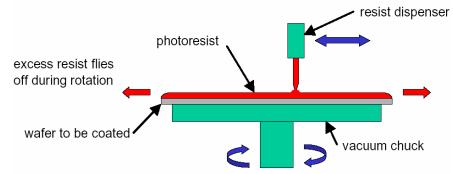

- **Patterning** covers the series of processes that shape or alter the existing shape of the deposited materials and is generally referred to as lithography. In conventional lithography, the wafer is coated with a chemical called a *photoresist*. The photoresist is exposed by a 'stepper', a machine that focuses, aligns, and moves the mask, exposing select portions of the wafer to short wavelength UV light. The unexposed regions are washed away by a developer solution. After etching or other processing, the remaining photoresist is removed by oxygen plasma ashing or stripping.

- **Modification** of electrical properties consists of doping transistor sources and drains in diffusion furnaces and by ion implantation. These doping processes are followed by furnace annealing or in advanced devices, by rapid thermal annealing which serve to activate the implanted dopants. Modification of electrical properties extends to reduction of the dielectric constant in low-k insulating materials via exposure to ultraviolet light.

# Processes forming and involved in forming semiconductor devices

# 1.1.1 Alloying

1.1

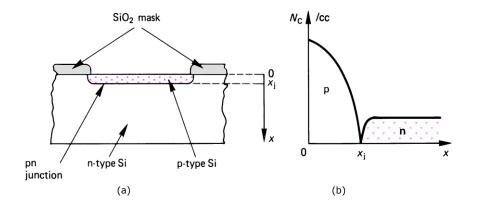

At the desired region on an n-type wafer, a small amount of p-type impurity is deposited. The wafer is then heated in an inert atmosphere and a thin film of melt forms on the interface. On gradual, slow cooling, a continuous crystalline structure results, having a step or abrupt pn junction as shown in figure 1.2. This process is not employed to form modern p-n junctions but can be used at the metallisation stage of wafer fabrication.

Figure 1.2. *n-Si* to At metal alloy junction: (a) cross-section where  $x_j$  is the junction depth below the metal-semiconductor boundary and (b) doping profile of the formed step junction.

# 1.1.2 Diffusion

Diffusion, the movement of a chemical species from a region of high concentration to a region of lower concentration, is one of the two major processes by which chemical dopants are introduced into a semiconductor (the other process being ion implantation). The controlled diffusion of dopants into silicon to alter the type and level of conductivity of semiconductor materials is the foundation of forming a p-n junction

and formation of devices during wafer fabrication, as shown in figure 1.3. It is used to form bases, emitters, and resistors in bipolar devices, as well as drains and sources in MOS devices. It is also used to dope polysilicon layers. It is not applicable to SiC processing.

Figure 1.3. Diffused pn junction: (a) cross-section where  $x_j$  is the junction depth below the silicon surface and (b) doping concentration profile.

The mathematics that govern the mass transport phenomena of diffusion is based on two concepts.

#### First Concept

Whenever an impurity concentration gradient,  $\partial C/\partial x$ , exists in a finite volume of a matrix substance (the silicon substrate in this context), the impurity material has a natural tendency to move in order to distribute itself more evenly within the matrix and decrease the concentration gradient.

Given time, this flow of impurities eventually results in homogeneity within the matrix, causing the net flow of impurities to stop. The mathematics of this transport mechanism is based on the flux, *J*, of material across a given plane is proportional to the concentration gradient across that plane. That is:

$$J = -D \frac{\partial N(x,t)}{\partial x}$$

(1.7)

where J is the flux,

$D = \mu kT$  is the diffusion constant or diffusivity for the material that is diffusing the solvent, m/s,

$\partial N(x,t) / \partial x$  is the concentration gradient. *k* is Boltzmann's constant, and  $\mu$  is ionic mobility.

The diffusion constant, *D*, of a material is also referred to as *diffusion coefficient* or *diffusivity* and is related to mobility,  $\mu$ , by  $D=\mu kT$ . It is expressed in units of length<sup>2</sup>/time, such as  $\mu m^2$ /hour. The negative sign of the right side of the equation indicates that the impurities flow to the lower concentration.

#### Second Concept

Equation (1.7) does not account for the fact that the gradient and local concentration of the impurities in a finite volume of material decreases with an increase in time, an aspect that is important to diffusion processes.

The flux  $J_1$  of impurities entering a section of a material with a concentration gradient is different from the flux  $J_2$  of impurities leaving the same section. From the law of conservation of matter, the difference between  $J_1$  and  $J_2$  must result in a change in the concentration of impurities within the section, assuming that no impurities are formed or consumed in the section.

The second concept states that the change in impurity concentration over time is equal to the change in local diffusion flux, or

$$\frac{\partial N(x,t)}{\partial t} = - \frac{\partial J(x,t)}{\partial x}$$

or, from the first concept, equation (1.7)

$$\frac{\partial N(x,t)}{\partial t} = \frac{\partial \left( D \frac{\partial N(x,t)}{\partial x} \right)}{\partial x}$$

(1.8)

If the diffusion coefficient is independent of position, such as when the impurity concentration is low, then the second concept may be simplified to:

$$\frac{\partial N(x,t)}{\partial t} = D \frac{\partial^2 N(x,t)}{\partial x^2}$$

(1.9)

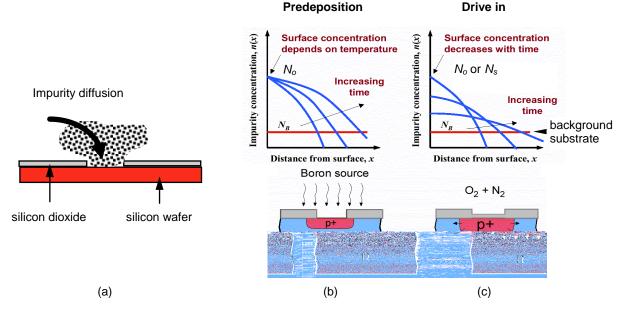

There are two major ways by which to deposit impurities into a substance by thermal diffusion. In the first method, known as *predeposition*, a flux of impurities continuously arrives at the surface of the substrate such that the concentration gradient of the impurity remains constant at the surface of the substrate, as shown in

figure 1.4b. In the second method, known as redistribution or *drive-in* diffusion, a thin layer of the impurity material is deposited on the substrate. In this case, the impurity gradient at the surface of the substrate decreases with time, as shown in figure 1.4c.

The semiconductor diffusion process is usually performed in two steps: predeposition and then drive-in.

- During *predeposition*, the impurity dopant is added to the wafer n-type silicon substrate. Predeposition is done in a diffusion furnace at temperatures around 1000 to 1250°C. The dopant is introduced into the furnace, and may be in the form of a gas, solid or liquid. Gaseous dopants are mixed with an inert carrier gas, such as nitrogen or argon, and introduced into the furnace. Solid dopants are often applied in a powder form. The solid is heated and a stream of carrier gas moves the dopant into the furnace. Liquid sources are used by bubbling an inert carrier gas through the liquid dopant, and the gas saturated with the liquid is added to the furnace. This compound breaks down as a result of the high temperature, and is slowly diffused into the substrate. The maximum impurity concentration occurs at the surface, tailing off towards the inside.

- The wafers are then put into a second furnace at higher temperatures (about 1300°C) to *drive-in* the dopant. The drive-in process usually occurs in an oxidizing atmosphere so that a protective layer of Si0<sub>2</sub> is grown over the diffused layer.

| Dopant state | Dopant type | dopant                                                         | chemistry                                                                                                           |  |  |

|--------------|-------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| gas          | p-type      | diborane B <sub>2</sub> H <sub>6</sub>                         | $B_2H_6 + 30_2 \rightarrow B_20_3 + 3H_20$                                                                          |  |  |

|              | n-type      | arsine AsH <sub>3</sub><br>phosphine PH <sub>3</sub>           | $\begin{array}{c} 2AsH_3 + 30_2 \rightarrow As_20_3 + 3H_20 \\ 2PH_3 + 40_2 \rightarrow B_20_5 + 3H_20 \end{array}$ |  |  |

| liquid       | p-type      | BBr <sub>3</sub>                                               | $4BBr_3 + 30_2 \rightarrow 2B_20_3 + 6Br_2$                                                                         |  |  |

|              | n-type      | AsCl <sub>3</sub> , P0Cl <sub>3</sub>                          | $4P0C\ell_3 + 30_2 \rightarrow 2P_20_5 + 6C\ell_2$                                                                  |  |  |

| solid        | p-type      | BN, B <sub>2</sub> O <sub>3</sub>                              | $2B_2O_3\text{+}3Si_4 \rightarrow 4B\text{+}3SiO_2$                                                                 |  |  |

|              | n-type      | As <sub>2</sub> 0 <sub>3</sub> , P <sub>2</sub> 0 <sub>5</sub> | $\begin{array}{c} 2As_20_3+3Si \rightarrow 4As+3Si0_2\\ 2P_2O_5+5Si_4 \rightarrow 4P+5SiO_2 \end{array}$            |  |  |

# Table 1.1: Dopants and chemical reactions

Typical dopants and silicon chemical reactions are shown in Table 1.1, while common diffusion coefficients and activation energies, referenced to 0 degree Kelvin, are shown in Table 1.2.

The diffusion process is a junction forming technique that is not applicable to silicon carbide, and other wide band gap material, wafer processing.

#### Figure 1.4. Diffusion processes:

(a) pictorial representation of mechanism; (b) predeposition diffusion; and (c) drive in diffusion.

The doping profile is mathematically defined and is varied by controlling the vapour mixture concentration, the furnace temperature, and time of diffusion.

If the source concentration is continuously replenished – *predeposition dose*, thus maintained constant, the surface concentration is  $N(0,t) = N_s$ ,  $(N(\infty,t) = 0)$ , and the initial concentration is N(x,0)=0, then the doping profile is given by a complementary error function, *erfc*.

$$N(x,t) = N_{s} \operatorname{erfc}\left(\frac{x}{2\sqrt{Dt}}\right)$$

$$= N_{s}\left(1 - \operatorname{erf}\left(\frac{x}{2\sqrt{Dt}}\right)\right) = N_{s}\left(1 - \operatorname{erf}\left(u\right)\right) = N_{s}\left(1 - \frac{2}{\sqrt{\pi}}\int_{0}^{u} e^{-v^{2}} dv\right)$$

(1.10)

where  $u = \frac{x}{2\sqrt{Dt}} = \frac{x}{\text{diffusion length}}$

The area under the diffusion profile is the total amount of dopant diffused into the wafer:

$$Q(t) = \int_{0}^{\infty} N(x,t) dx = \frac{2}{\sqrt{\pi}} N_{s} \sqrt{Dt} = 1.13 N_{s} \sqrt{Dt}$$

(1.11)

The junction depth is where the doping profile N(x,t) equals the background doping  $N_B$  level, that is

$$N(x_j, t) = N_s \operatorname{erfc}\left(\frac{x_j}{2\sqrt{Dt}}\right) = N_B$$

Rearranging, gives the junction depth  $x_i$  as

$$X_{j} = 2\sqrt{Dt} \times erfc^{-1} \frac{N_{B}}{N_{s}}$$

(1.12)

If natural dopant depletion occurs – *drive in*, that is the initial dose *S* at the surface is not replenished, then the profile is an exponential function, which gives a Gaussian diffusion distribution.

$$N(x,t) = \frac{S}{\sqrt{\pi Dt}} e^{-\frac{x^2}{4Dt}}$$

(1.13)

where

$$\int_{o} N(x,t) dx = S = \text{non-replenished initial surface dose}$$

(1.14)

The diffusion length,  $x=2\sqrt{Dt}$ , is an approximate measure of how far the dopant has diffused, which is the distance from the surface to where the concentration has fallen to 1/e, 36.8%.

The surface concentration, which is not replenished (dN(0,t)/dx = 0), diminishes with time, according to

$$W(0,t) = \frac{S}{\sqrt{\pi Dt}}$$

(1.15)

The junction depth is where the doping profile N(x,t) equals the background doping  $N_B$  level, that is

$$N(x_j,t) = \frac{S}{\sqrt{\pi Dt}} e^{-\frac{X^2}{4Dt}} = N_B$$

Rearranging, gives the junction depth  $x_i$  as

$$x_{j} = 2\sqrt{Dt} \times \left( \ell n \frac{S}{\sqrt{\pi Dt} N_{B}} \right)^{V_{2}} = 2\sqrt{Dt} \times \left( \ell n \frac{N(0,t)}{N_{B}} \right)^{V_{2}}$$

(1.16)

In both processing cases,  $N(\infty, t) = 0$ .

The gradient of the diffusion profile is obtained by differentiating equation (1.13):

$$\frac{dN(x,t)}{dt} = -\frac{x}{2Dt}N(x,t)$$

(1.17)

The gradient is zero at x = 0 and  $x = \infty$ , and the maximum gradient occurs at  $x=\sqrt{2Dt}$ . Diffusivity *D* varies with temperature according to

$$D = D_{a} e^{-\frac{L_{a}}{kT}}$$

(1.18)

where  $D_o = \text{diffusion coefficient}$  (in cm<sup>2</sup>/s) extrapolated to infinite temperature

$E_a$  = activation or threshold energy in eV, which is not particularly temperature dependant. For multiple diffusions, the effective  $Dt_{effective}$  equals the sum of each diffusion process Dt.

#### Table 1.2: Typical diffusion coefficients and activation energies at 0K

|     | Do                 | E <sub>a</sub>                                                                            |

|-----|--------------------|-------------------------------------------------------------------------------------------|

| 0 K | cm <sup>2</sup> /s | eV                                                                                        |

| В   | 1.0                | 3.50                                                                                      |

| Р   | 4.7                | 3.68                                                                                      |

| At  | 4.58               | 3.88                                                                                      |

| As  | 9.17               | 3.99                                                                                      |

| In  | 1.20               | 3.50                                                                                      |

|     | B<br>P<br>At<br>As | B         1.0           P         4.7           At         4.58           As         9.17 |

# **Example 1.2:** Constant Surface Concentration diffusion - predeposition

For a constant-source boron diffusion into n-type  $10^{15}$  cm<sup>-3</sup> silicon at 1000°C, the surface concentration is maintained at  $10^{19}$  cm<sup>-3</sup> and the diffusion time is 1 hour. Find

- *i.* Total amount of dopant diffused, Q(t) and the gradient at x = 0 and

- *ii.* The gradient and location (junction depth) where the dopant concentration reaches 10<sup>15</sup> cm<sup>-3</sup>.

#### Solution

Using data for boron in Table 1.2, equation (1.18) gives the diffusion coefficient of boron at 1000°C as

$$D = D_o e^{-\frac{E_o}{kT}} = 24e^{-\frac{3.05}{8.614 \times 10^{-5} \times 1273}} = 1.39 \times 10^{-14} \,\mathrm{cm}^2/\mathrm{s}$$

so the diffusion length is

$$\sqrt{Dt} = \sqrt{1.39 \times 10^{-14} \times 3600} = 7.07 \times 10^{-6} \text{ cm}$$

i. The area under the diffusion profile from equation (1.11) is

$$Q(t) = 1.13N_{s}\sqrt{Dt} = 1.13 \times 10^{19} \times 7.07 \times 10^{-6} = 8.0 \times 10^{13} \,\mathrm{cm}^{-2}$$

$$\frac{dN}{dx}\Big|_{x=0} = -\frac{N_{s}}{\sqrt{\pi Dt}} = -\frac{10^{19}}{\sqrt{\pi} \times 7.07 \times 10^{-6}} = -7.98 \times 10^{23} \,\mathrm{cm}^{-4}$$

ii. From equation (1.10) rearranged, when  $N_B = 10^{15}$  cm<sup>-3</sup>, the junction depth  $x_i$  is given by

$$x_{j} = 2\sqrt{Dt} \times erfc^{-1} \left(\frac{N_{B}}{N_{s}}\right) = 2\sqrt{Dt} \times erfc^{-1} \left(\frac{10^{15}}{10^{19}}\right)$$

$$= 2 \times 7.07 \times 10^{-6} \times 2.75 = 0.389 \,\mu\text{m}$$

$$\frac{dN}{dx}\Big|_{x=0.389 \,\mu\text{m}} = -\frac{N_{s}}{\sqrt{\pi Dt}} e^{-\frac{x^{2}}{4Dt}} = -4.0 \times 10^{20} \,\text{cm}^{-4}$$

Example 1.3: Constant Total Dopant diffusion – drive in - #1

Arsenic was pre-deposited by arsine gas, and the resulting dopant per unit area was  $10^{14}$  cm<sup>-2</sup>. How long would it take to drive the arsenic in to  $x_j = 1 \mu m$ ? Assume a background doping of  $N_{sub} = 10^{15}$  cm<sup>-3</sup>, and a drive-in temperature of 1200°C. For As, assume  $D_o = 24$  cm<sup>2</sup>/s, and  $E_a = 4.08$  eV at 1200°C.

#### Solution

From equation (1.18) the diffusion coefficient for arsenic at 1200°C is

$$D = D_{o}e^{-\frac{E_{a}}{kT}} = 24 \times e^{-\frac{4.08}{8.614 \times 10^{-5} \times 1473}} = 2.602 \times 10^{-13}$$

Rearranging equation (1.13) gives

$$x_{j}^{2} = 10^{-8} = 4Dt \times \ell \ln\left(\frac{S}{N_{B}\sqrt{\pi Dt}}\right) = 1.04 \times 10^{-12}t \times \ell \ln\left(\frac{1.106 \times 10^{5}}{\sqrt{t}}\right)$$

That is

$t \times ln t - 23.22t + 19230 = 0$ An iterative solution gives t=1191.7s or approximately 19.9 minutes.

#### Example 1.4: Constant Total Dopant diffusion – drive in - #2

An arsenic constant-dose diffusion is performed with an initial dose of  $S=10^{14}$  cm<sup>-2</sup>. The diffusion temperature is 1100°C for 2 hours. The starting wafer had a p-type substrate background doping of  $10^{17}$  cm<sup>-3</sup>. Find the concentration of the As at the surface and find the junction depth.

#### Solution

From Table 1.2

$$D = D_o e^{-\frac{E_a}{kT}} = 9.17 e^{-\frac{3.99}{8.614 \times 10^{-5} \times 1100 + 273}} = 2.07 \times 10^{-14} \text{ cm}^2/\text{s}$$

Then the diffusion length is

$$\sqrt{Dt} = \sqrt{2.07 \times 10^{-14} \times 7200} = 1.22 \times 10^{-5} \text{ cm}$$

The surface concentration is

$$\frac{dN}{dx}\Big|_{x=0} = N_o = \frac{N_s}{\sqrt{\pi Dt}} = \frac{10^{18}}{\sqrt{\pi} \times 1.22 \times 10^{-5}} = 4.6 \times 10^{18} \text{ cm}^{-3}$$

From equation (1.13) rearranged, the junction depth for Gaussian diffusions is

$$x_{j} = 2\sqrt{Dt} \ell n \left(\frac{N_{o}}{N_{B}}\right)^{2}$$

$$= 2 \times 1.22 \times 10^{-5} \text{ cm} \times \ell n \left(\frac{4.6 \times 10^{18} \text{ cm}^{-3}}{10^{17} \text{ cm}^{-3}}\right)^{\frac{1}{2}}$$

$$= 0.467 \mu \text{m}$$

#### 1.1.3 Epitaxy growth - deposition

*Epitaxy* or epitaxial growth is the process of depositing a non-volatile, thin solid layer typically 0.5 to 100  $\mu$ m, of single crystal material over a single crystal substrate. (Also see sections 1.2.1 and 1.2.2)

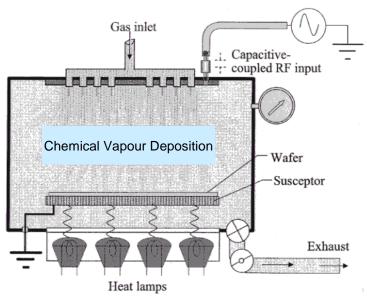

#### Chemical Vapour Deposition (CVD) (see section 1.2.1)

Epitaxial growth is usually achieved using chemical vapour deposition (CVD). (Specifically, Metal-Organic Chemical Vapour Deposition, MOCVD or Metal-Organic Vapour Phase Epitaxy, MOVPE) The semiconductor deposited film is often the same material as the substrate, and the process is known as homoepitaxy, or simply, epi, as with silicon deposition on a silicon substrate. If the substrate is an ordered semiconductor crystal (that is mono-silicon, gallium arsenide), the process continues building on the substrate with the same crystallographic orientation, with the substrate acting as a seed for the deposition. If an amorphous/polycrystalline substrate surface is used, the film will also be amorphous or polycrystalline. A key feature of epitaxy is that a lightly doped layer of epitaxial silicon can be grown upon a heavily doped silicon substrate, thus creating a layer of differing conductivity that can serve as an insulating layer or intrinsic buffer region. Chemical vapour deposition CVD (see section 1.2.1) of silicon epitaxy occurs in an epitaxial reactor that consists of a quartz induction heated reaction chamber into which a susceptor is placed. The susceptor has two functions:

- mechanical support for the wafers and

- an environment with uniform thermal distribution.

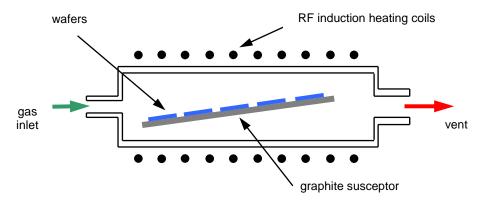

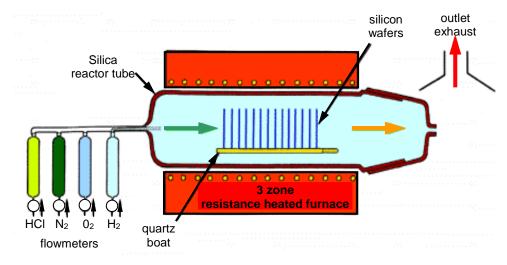

The technological method of introducing reactant gases with only the substrates heated inside a reactor is called Vapour Phase Epitaxy, a schematic of which is shown in figure 1.5.

A possible fabrication process is as follows. A pre-cleaned, polished, near perfect silicon crystal surface acts as a substrate for subsequent deposition. Usually hydrogen chloride is used to etch the wafers. The pre-doped silicon is heated to about 1150°C in a quartz reactor tube at atmospheric pressure. A hydrogen gas flow carrying a compound of silicon such as silicon tetrachloride SiCl<sub>4</sub> or silane SiH<sub>4</sub> is passed over the hot substrate surface, and silicon atoms are deposited, growing a new continuous lattice. If phosphine (PH<sub>3</sub>) arsine (AsH<sub>3</sub>) or diborane (B<sub>2</sub>H<sub>6</sub>) is included in the silicon compound carrier gas flow of H<sub>2</sub> and N<sub>2</sub>, a layer of the required doping type and resistivity occurs. Up to 100µm of doped silicon can be grown on substrates for power devices at a high growth rate of about 1 µm/min at 1200°C. A ultra low crystalline fault rate is essential if uniform electrical properties are to be attained. Selective deposition, depending on the substrate surface masking, is possible.

Figure 1.5. Typical cold-wall vapour phase epitaxial reactor.

There are four major chemical sources of silicon for epitaxial deposition:

- silane, SiH<sub>4</sub>, as per equation (1.19)

- silicon tetrachloride, SiCl<sub>4</sub>, as per equation (1.22);

- trichlorosilane, SiHCl<sub>3</sub>, as per equation (1.20); and

- dichlorosilane,  $SiH_2Cl_2$ , as per equation (1.21).

Chemical reaction equations can describe the growth of epitaxial layers. Each of the chemical sources mentioned can be described by an over-all reaction equation that shows how the vapour phase reactants form the silicon epitaxial film. For example, the over-all pyrolytic reaction for silicon epitaxy by silane decomposition reaction is:

$$SiH_4 \rightarrow Si + 2H_2$$

(at 1000°C to 1100°C) (1.19)

Hydrogen reduction of trichlorosilane is

$$SiHC\ell_3 + H_2 \to Si + 3HC\ell \tag{1.20}$$

Reduction of dichlorosilane is

$$SiH_2C\ell_2 \rightarrow Si + 2HC\ell$$

(1.21)

However, such over-all reaction equations do not describe the complete CVD process as to how the gas phase reactants interact or how the epi species are adsorbed on the substrate surface. For instance, the over-all reaction for the hydrogen reduction of silicon tetrachloride  $SiCl_4$  to form a silicon epitaxial layer is as follows:

$SiC\ell_4 + 2H_2 \rightarrow Si + 4 HC\ell$  (at 1150°C to 1300°C) (1.22)

However, intermediate chemical species such as SiHC $l_3$  and SiH<sub>2</sub>C $l_2$  are present during the silicon epitaxial growth:

$$\begin{aligned} SiC\ell_{4} &+ H_{2} \leftrightarrow SiHC\ell_{3} + HC\ell \\ SiHC\ell_{3} &+ H_{2} \leftrightarrow SiH_{2}C\ell_{2} + HC\ell \\ SiH_{2}C\ell_{2} \leftrightarrow SiC\ell_{2} + H_{2} \\ SiHC\ell_{3} \leftrightarrow SiC\ell_{2} + HC\ell \\ SiC\ell_{2} + H_{2} \leftrightarrow Si + 2HC\ell \end{aligned}$$

These equations illustrate that even if a given process is described by a single over-all reaction, the process is actually a combination of many simultaneous chemical reactions.

The growth rate of an epitaxial layer depends on several factors:

- the chemical sources;

- the deposition temperature; and

- the mole fraction of reactants.

Silicon epitaxy improves the performance of bipolar devices. By growing a lightly doped epi-layer over a heavily-doped silicon substrate, a higher breakdown voltage across the collector-substrate junction is achieved while maintaining low collector resistance. Lower collector resistance allows a higher operating speed with the same current. Epitaxy is also used in IC fabrication. By fabricating a CMOS device on a thin (3 to 7 microns) lightly doped epi layer grown over a heavily-doped substrate, latch-up occurrence is minimized – a phenomena applicable to power devices such as the MOSFET and IGBT.

As well as improving device performance, epitaxy also allows better control of doping concentrations within devices. The layer can also be made oxygen and carbon free. The disadvantages of epitaxy include higher cost of wafer fabrication, additional process complexities, and problems associated with growth defects in the epi-layer.

# Molecular Beam Epitaxy (MBE) (see section 1.2.2)

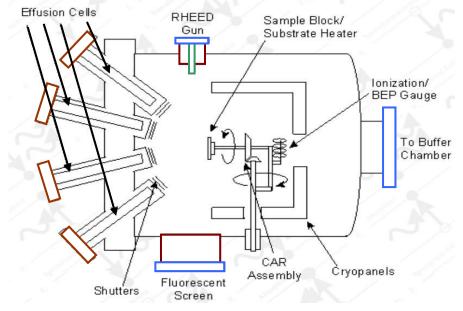

A schematic diagram of an MBE machine is shown in Figure 1.6. Generally, such machines consists of three vacuum sections, of which the growth chamber is the most important. The buffer section is involved in the preparation and storage of the wafers before entering the growth chamber. The load lock is used to insert and remove samples while retaining vacuum integrity. Samples are loaded onto a rotational magnetic holder known as, Continual Azimuthal Rotation (CAR). Cyropanels are used in conjunction with the vacuum system to keep the partial pressure of undesirable gases such as CO2 and H2O around 10-11 Torr. The principle of operation is that gaseous substances are bound to the cold surfaces within the pump by means of cryocondensation, cryosorption or cryotrapping. Epitaxial growth starts with the many heated cells, called effusion cells or *Knudsen* cells that contain a compound of the particular atomic species to be added into the vacuum chamber. Each source is independently heated until atoms of the source material are able escape by thermionic emission. An advancement of MBE, Gas Source MBE (GSMBE), uses room temperature gases for the source materials, thus avoiding contamination problems and high substrate temperatures that can cause segregation of dopant atoms.

Within the ultra-high vacuum, the free atoms have a long mean-free path and collisions with other atoms are infrequent. Atoms from the sources are able to travel in a straight line until they collide with the substrate material. A computer remotely operates the shutter controls, allowing the emission of different atom species to be directed at the substrate. The typical rate of growth with MBE is around a single mono-layer per second. Although slow, this allows for abrupt changes in material composition. Under proper conditions, the beam of atoms will attach to the substrate material and an epitaxial layer will begin to form.

Figure 1.6. Schematic diagram of MBE machine.

Thickness control is determined using an ion gauge mounted facing the beam sources. The Beam Equivalent Pressure (BEP) of the material sources measures the rate of layer growth. Alternatively, Reflection High-Energy Electron Diffraction (RHEED) is another measuring technique. Electrons are emitted from an electron gun at a glancing incidence to the CAR. The reflected and diffracted electrons emit light in a distinctive pattern when striking a phosphor screen. Starting from a flat substrate, the electrons are not scattered greatly and are recorded as an intense beam. As material is deposited on the surface, the atoms create islands of epitaxial growth with an associated material surface reflectivity decrease as the electrons are scattered. As the deposition process continues, material builds up on the surface, the islands join and create new flat surfaces with the original substrate becoming voids in the newly created material. As further material forms, the voids begin to fill and the reflectivity increases once again, not reaching the initial value, since the process of deposition is random and the surface never regains the flat profile of the initial polished substrate. By monitoring the oscillations in the reflectivity, thickness and growth rate of the epitaxial material can be estimated.

# 1.1.4 Ion-implantation and damage annealing

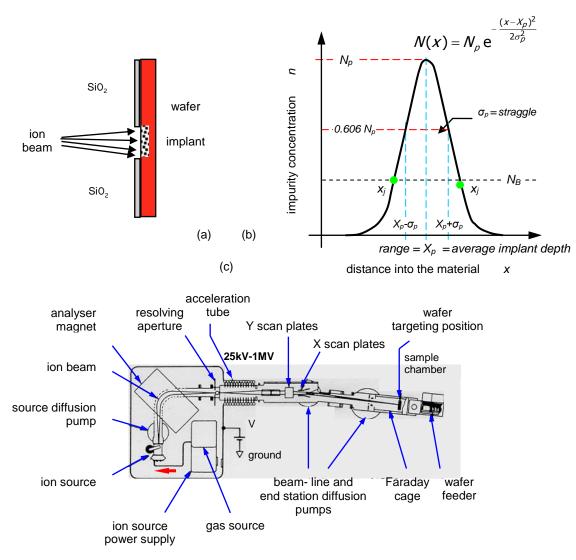

*Ion Implantation* is the process of depositing chemical dopant species (atoms stripped of electrons) into a substrate by directly bombarding the substrate with high-energy ions of the chemical being deposited, as shown in figure 1.7.

Diffusion and ion implant are the two major processes by which chemical species or dopants are introduced into a semiconductor such as silicon to form electronic structures. The advantage of ion implant over diffusion is its more precise control for depositing dopant atoms into the substrate (10<sup>11</sup> to 10<sup>18</sup> cm<sup>-2</sup>), giving excellent doping level uniformity and production repeatability.

The implanted profile shown in figure 1.7b, where two junctions may be formed, can be approximated by a Gaussian distribution function, which is similar to equation (1.13):

$$N(x) = \frac{S}{\sqrt{2\pi} \sigma_{\rho}} e^{-\frac{(x-X_{\rho})^{2}}{2\sigma_{\rho}^{2}}} = N_{\rho} e^{-\frac{(x-X_{\rho})^{2}}{2\sigma_{\rho}^{2}}}$$

(1.23)

where  $S = ion dose per unit area, cm^{-2}$

$\sigma_p$  = symmetrical standard deviation, *straggle*, in the projected range of the implanted ions, cm The depth of average or mean projected *range* (peak) is at  $X_p$  along the axis of incidence, where the maximum concentration occurs.

$$S = \frac{1}{q} \int_{o}^{t} I_{beam}(t') dt' = \frac{\frac{100 \text{ beam current (A)}}{q} \times \text{ implant time}}{\frac{q}{1.24}}$$

(1.24)

Figure 1.7. Ion implantation:

(a) pictorial representation of mechanism; (b) implanted ion distribution; and (c) implanting system.

The point where the diffused impurity profiles intersects the background concentration  $N_B$  is the metallurgical junction depth,  $x_i$ , where the net impurity concentration is zero. From equation (1.23)

$$N_{\beta} = N(x) = N_{\rho} e^{-\frac{(x_{j} - X_{\rho})^{2}}{2\sigma_{\rho}^{2}}} \quad \text{re-arranged gives}$$

$$x_{j} = X_{\rho} \pm \sigma_{\rho} \sqrt{2 \ell n \frac{N_{\rho}}{N_{\beta}}} \quad (1.25)$$

where  $N_{\rho} = S / \sqrt{2\pi} \sigma_{\rho}$  is the peak concentration.

Doping, which is the primary purpose of ion implanting, is used to alter the type and level of conductivity of semiconductor materials. It is used to form bases, emitters, and resistors in bipolar devices, as well as drains and sources in MOS devices. It is also used to dope polysilicon layers.

Typically, a gaseous dopant is ionized by electric discharge or by heat from a hot filament. The ions are separated using an electromagnetic field that bends the positively-charged particles to a selected band. This ion band is then passed through a high-current accelerator. The high-velocity beam of ions is focused on the wafer, causing the dopant ions to strike the wafer surface and penetrate. Sometimes a mask is used to implant a designated pattern on the wafer. As with diffusion, ion implantation allows the formation of junctions by changing the conductivity characteristics of precise regions in the wafer.

The basic procedure for ion implantation into silicon is as follows:

Ion impurities (B, P or As) are vaporised and accelerated by an electric field in a vacuum at high keV energies at the pre-doped silicon substrate, which is at room temperature. The ions penetrate the lattice to less than a few microns, typically 1µm at about ½ MeV. The resultant implanted doping profile is Gaussian, with the smaller ion like boron, penetrating deeper.

These high-energy atoms enter the crystal lattice and lose their energy by colliding with silicon atoms before finally coming to rest at some depth. Adjusting the acceleration energy controls the average deposition depth of the impurity atoms. Heat treatment is subsequently used to anneal or repair the crystal lattice disturbances caused by the atomic collisions.

Every implanted ion collides with several target atoms before it comes to rest. Such collisions may involve the nucleus of the target atom or one of its electrons. The total power of a target to stop an ion, or its total stopping power  $S_T$ , is the sum of the stopping power of the nucleus and the stopping power of the electron. Stopping power is described as the energy loss of the ion per unit path length of the ion.

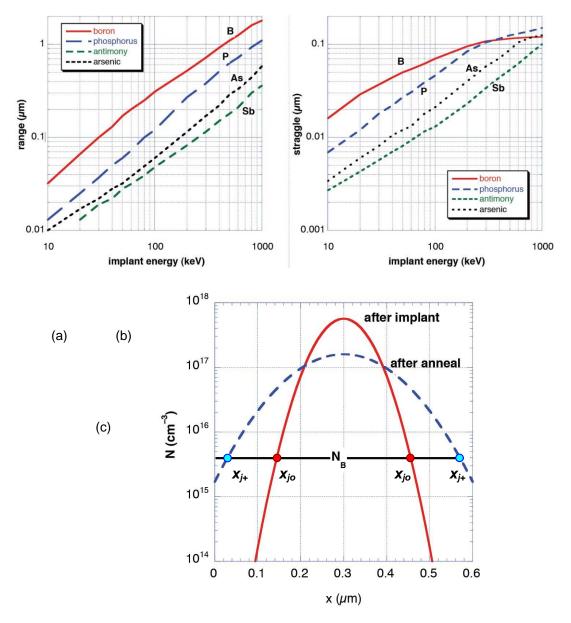

Implantation energies are typically 10keV to 1MeV, giving ion distributions with depths of 10 nm to 10 µm from doses vary from 10<sup>12</sup> ions/cm<sup>2</sup> for threshold voltage adjustment in MOSFETs to 10<sup>18</sup> ions/cm<sup>2</sup> for the formation of buried insulating layers. Figures 1.8a and 1.8b show implant energy characteristics of typical dopants in silicon.

Figure 1.8. Ion implanted silicon: (a) range  $X_p$  dependency on energy; (b) straggle  $\sigma_p$  dependency on energy; and (c) typical junction change after annealing.

The damage caused by atomic collisions and bombardment during high-energy ion implantation changes the material structure therefore electrical characteristics of the target substrate. Many target atoms are displaced, creating deep electron and hole traps which capture mobile carriers and increase resistivity. *Annealing* is therefore needed to repair the lattice damage and put dopant atoms in substitutional sites where they can be electrically active again.

Annealing can be considered as apart of a drive-in Gaussian diffusion process, where the effective *Dt* of the implant process is  $\frac{1}{2}\sigma_a^2$ , which produces a profile following annealing given by

$$N(x) = \frac{S}{\sqrt{2\pi \left(\sigma_{\rho}^{2} + 2Dt\right)}} e^{-\frac{(x-X_{\rho})^{2}}{2\sigma_{\rho}^{2} + 4Dt}} = N_{\rho}^{*} \times e^{-\frac{(x-X_{\rho})^{2}}{2\sigma_{\rho}^{2} + 4Dt}}$$

(1.26)

The peak concentration  $N_{\rho}^*$  decreases but its depth is unchanged, and the deviation increases, as illustrated in figure 1.8c.

Silicon damage caused by ion implantation includes:

- the formation of crystal defects such as Frenkel defects, vacancies, di-vacancies, higher-order vacancies, and interstitials;

- the creation of local zones of amorphous material within the supposedly crystalline structure

- formation of continuous amorphous layers as the localized amorphous regions grow and overlap; and

- microscopic sputtering and directional non-linear ion channelling.

The first two damage types are categorized as 'primary crystalline damage'. Restoring the ion-implanted substrate to its pre-implant condition requires the substrate being subjected to a reparative thermal process known as *annealing*.

Ion implantation damage annealing has five major components:

- electrical activation of the implanted impurities;

- primary crystalline damage annealing;

- annealing of continuous amorphous layers;

- dynamic annealing; and

- diffusion of implanted impurities.

Annealing is conducted in a neutral environment, such as in Ar or a N<sub>2</sub> atmosphere in a stack furnace.

Electrical activation of the implanted impurities refers to the process of increasing the electrical activity of newly implanted impurity atoms during annealing, which usually do not occupy substitutional sites after being implanted. Temperatures up to 500°C remove trapping defects, releasing carriers to the valence or conduction bands in the process. Electrical activity decreases again at 500 to 600°C, because of the formation of dislocations. Beyond 600°C, electrical activation increases until a peak at 800 to 1000°C.

In summary, primary crystalline damage annealing consists of:

- recombination of vacancies and self-interstitials in the low temperature range, up to 500°C;

- formation of dislocations at 500 to 600°C which can capture impurity atoms; and

- dissolution of these dislocations at 900 to 1000°C.

Annealing of the continuous amorphous layers that extend to the surface occur by solid-phase epitaxy between 500 to 600°C. The crystalline substrate beneath the amorphous layers initiates the recrystallization of the amorphous layers, with the regrowth proceeding towards the substrate surface. Factors affecting the recrystallization rate include crystal orientation and the implanted impurities. Amorphous layers that do not extend to the surface anneal differently, with the solid-phase epitaxy occurring at both amorphous-single crystal interfaces and the regrowth interfaces meeting below the surface.

Dynamic annealing effects refers to the healing of implant damage while the implantation process is occurring. This takes place because the heat applied to the wafer during implantation makes the point defects more mobile.

Diffusion of implanted impurities relates to the mass transport of implanted species across a concentration gradient within an implanted layer during the annealing process. The presence of implant damage makes this diffusion process more complex than what occurs in an undamaged single-crystal substrate. Diffusion of implanted impurities during annealing degrades devices that have shallow junctions or narrow base and emitter regions if the thermal processing is not rapid enough, particularly in the case of boron ion implantation.

# Example 1.5: Ion implantation

For a 100 keV boron implant with a dose of  $S = 5 \times 10^{14}$  cm<sup>-2</sup>, calculate

- i. the peak concentration,

- ii. the junction depth, if the substrate phosphorus background doping level is 10<sup>15</sup> /cm<sup>3</sup>, and

- iii. the surface concentration.

- iv. the junction depths after annealing for 30 minutes at 1000°C.

# Solution

From figure 1.8 parts a and b, for a 100keV boron implant, the peak concentration occurs at a depth (range) of  $X_p = 0.31 \,\mu\text{m}$  and the ion implant standard deviation (straggle) is  $\sigma_p = 0.07 \,\mu\text{m}$ .

i. From equation (1.23)

$$N(x) = \frac{S}{\sqrt{2\pi} \sigma_p} e^{-\frac{(x-X_p)^2}{2\sigma_p^2}}$$

Differentiation gives

$$\frac{dn}{dx} = -\frac{S}{\sqrt{2\pi}\sigma_p} \frac{2(x-X_p)}{2\sigma_p^2} e^{\frac{(x-X_p)^2}{2\sigma_p^2}} = 0$$

which confirms that the maximum concentration occurs when  $x = X_p$ . Substitution into equation (1.23) gives the concentration  $N(x = X_p = 0.31 \ \mu\text{m}) = 2.85 \times 10^{18} \text{ cm}^{-3}$ .

ii. The junction depth, with a background doping level of  $10^{15}$  /cm<sup>3</sup>, is given by equation (1.25) , that is

$$X_{j} = X_{\rho} \pm \sigma_{\rho} \sqrt{2 \ell n \frac{N_{\rho}}{N_{\beta}}}$$

$$= 0.31 \pm 0.07 \sqrt{2 \ell n \frac{2.85 \times 10^{18}}{10^{15}}} = 0.31 \pm 0.28 \mu m$$

Two junctions are formed, at 0.03  $\mu$ m and 0.59  $\mu$ m below the incident surface.

iii. Since the ion implant has formed two junctions within the n-substrate, the surface concentration is dominated by the background doping level of the substrate, 10<sup>15</sup> /cm<sup>3</sup>. The surface ion implant doping is given by equation (1.23)

$$N(x=0) = \frac{S}{\sqrt{2\pi}\sigma_{p}} e^{-\frac{X_{p}^{2}}{2\sigma_{p}^{2}}} = 2.85 \times 10^{18} \times e^{-\frac{0.31^{2}}{2\times0.07^{2}}} = 1.57 \times 10^{14} / \text{cm}^{3}$$

The n-type surface concentration is  $10^{15}$  /cm<sup>3</sup> –  $1.57 \times 10^{14}$  /cm<sup>3</sup> =  $8.43 \times 10^{14}$  /cm<sup>3</sup>.

iv. For heat treatment, from example 1.2,  $Dt = 1.39 \times 10^{-14} \text{ cm}^2/\text{s} \times 30 \times 60 \text{s} = 2.5 \times 10^{-11} \text{ cm}^2$ . Equating equation (1.26) to the background concentration  $10^{15} / \text{cm}^3$

$$N_{B} = \frac{S}{\sqrt{2\pi \left(\sigma_{p}^{2} + 2Dt\right)}} e^{-\frac{(x-X_{p})}{2\sigma_{p}^{2}+4L}}$$

$$10^{15} \text{ cm}^{-3} = \frac{5 \times 10^{14} \text{ cm}^{-2}}{\sqrt{2\pi \left( \left(7 \times 10^{-6} \text{ cm}\right)^2 + 2 \times 2.5 \times 10^{-11} \text{ cm}^2 \right)}} e^{-\frac{(x-31\mu\text{m})^2}{2\times \left( \left(7 \times 10^{-6} \text{ cm}\right)^2 + 2 \times 2.5 \times 10^{-11} \text{ cm}^2 \right)}}$$

yields junction depths

$$x_{j} = 0.31 \mu m \pm 0.44 \mu m$$

The implant after annealing reaches the surface, resulting in one p-n junction 0.75um below the surface. The peak concentration  $N_{\rho}^{*}$  at 0.31µm is 2 x 10<sup>18</sup> cm<sup>-3</sup>.

#### 1.2 Thin film deposition

A thin film is a layer with a high surface area-to-volume ratio. Thin films are extensively used to apply dopants and sealants to wafers and microelectronic parts, and can be a resistor, a conductor, an insulator or a semiconductor. Thin films can be deposited with a thickness of between a few nanometres to about 100µm. The film can subsequently be locally etched using processes described in the Lithography and Etching sections of this chapter, sections 1.5 and 1.6, respectively.

Thins films behave differently from bulk materials of the same chemical composition in several ways. Thin films are sensitive to surface properties while bulk materials generally are not. Thin films are also more sensitive to thermo-mechanical stresses. Thin film integrity is influenced by the quality of its adhesion to and conformal coverage of the underlying layer, residual or intrinsic stresses after deposition, and the presence of surface imperfections such as pinholes.

The adhesion of a thin film to the substrate or underlying layer is paramount to ensuring thin film reliability. A thin film that is initially adhering to the underlying layer may lift off after the device is subjected to

thermo-mechanical stresses. Reliable thin film adhesion depends on the cleanliness of the surface upon which it is deposited. Optimum substrate roughness also affects thin film adhesion. An ultra-smooth substrate decreases adhesion tendency. A rough substrate on the other hand can result in coating defects, which can also lead to thin film adhesion failures.

Regardless of the deposition process, thin films always have an intrinsic stress that can be either tensile or compressive. High residual stresses can lead to adhesion problems, corrosion, cracking, and deviations in electrical properties. Thus, proper deposition is critical to minimize intrinsic stresses in thin films.

Deposition technology is classified into two reaction types, viz. chemical and physical:

- *i.* Depositions that result because of a chemical reaction:

- Chemical Vapour Deposition (CVD) [also see section 1.1.3]

- Electrodeposition

- Epitaxy

- Thermal oxidation

These processes exploit the creation of solid materials directly from chemical reactions in gas and/or liquid compositions or with the substrate material. The solid material is usually not the only product formed by the reaction. By-products can include gases, liquids and other solids.

- *ii.* Depositions that result because of a physical reaction:

- Physical Vapour Deposition (PVD) [also see section 1.1.3]

- Casting

Common to these processes is that the material deposited is physically moved onto the substrate. In other words, there is no chemical reaction that forms the material on the substrate. This is not completely correct for casting processes, though it is more convenient to classify them as physical.

Whether the process is physical or chemical, the processing deposition reactor uses either:

- a cold wall system, where the heating process uses radio frequency or infra red heating, while

- a *hot wall* system uses a thermal heating resistive element or series of elements forming heating zones.

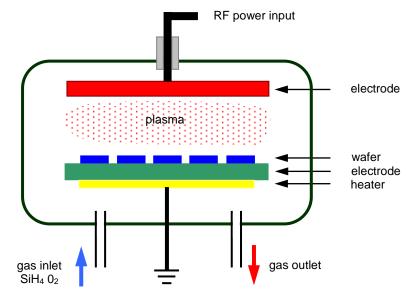

# 1.2.1 Chemical Vapour Deposition (CVD)

A fluid precursor undergoes a chemical change at a solid surface, leaving a solid layer.

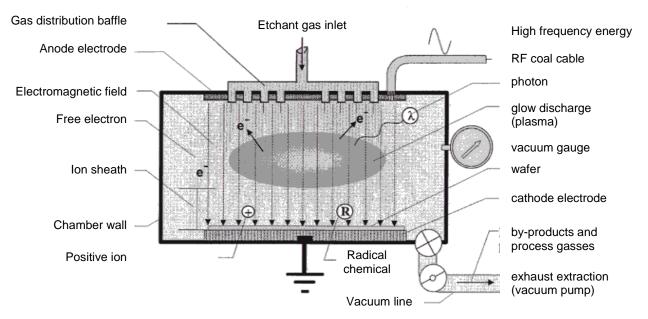

In this process, the substrate is placed inside a reactor into which a number of gases are supplied, as shown in figure 1.9. The principle of the process is that a chemical reaction occurs between the source gases, with the solid material product of that reaction condensing on all surfaces inside the reactor.

CVD is capable of producing thick, dense, ductile, and good adhesive coatings on metals and non-metals such as glass and plastic. In contrast to PVD coating in the 'line of sight', CVD can simultaneously coat all surfaces of the substrate. The thin films from chemical deposition techniques tend to be conformal, rather than directional.

Figure 1.9. Typical CVD processing reactor system.

CVD processes are used to produce a thin film with good step coverage. A variety of materials can be deposited, however, some form hazardous by-products during processing. The quality of the material varies from process to process, however generally a higher process temperature yields a material with higher quality and fewer defects. They are generally not suitable for mixtures of materials. CVD processing is not possible for some materials; there is no suitable chemical reaction.

Chemical deposition is categorized by the phase of the precursor:

- Plating relies on liquid precursors, often a solution of water with a salt of the metal to be deposited. Some plating processes are driven only by reagents in the solution (usually for noble metals), but the most important process is electroplating. Although not commonly in semi-conductor processing, it has resurfaced with the use of chemical-mechanical polishing.

- Conventional CVD coating processing requires a metal compound that will volatilize at a low temperature and decompose to a metal when it contacts the substrate at higher temperature. An example of CVD is nickel carbonyl (NiCO<sub>4</sub>) coating, as thick as 2.5 mm, on glass windows and containers to make them explosion or shatter resistant.

- Diamond CVD coating processing is used to increase the surface hardness of cutting tools. The process is performed at temperatures higher than 700°C which softens most tool steels. Thus, the application of diamond CVD is limited to materials which do not soften at this temperature, such as cemented carbides.

- Plasma-assisted CVD coating processing is performed at lower temperature than diamond CVD coating. Diamond coatings or silicon carbide barrier coatings are applied on plastic films and semiconductors, including sub-¼µm semiconductors.

- Chemical solution deposition uses a liquid precursor, usually a solution of organometallic powders dissolved in an organic solvent. This is a relatively inexpensive, simple thin film process that is able to produce stoichiometrically accurate crystalline phases.

- Chemical vapour deposition generally uses a gas-phase precursor, often a halide or hydride of the element to be deposited. In the case of metal-organic CVD, an organometallic gas is used.

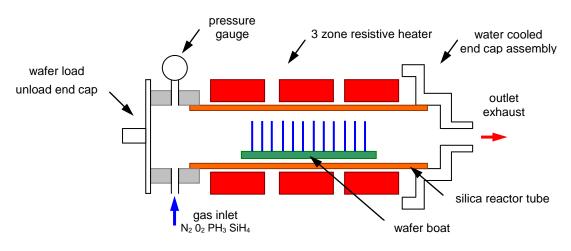

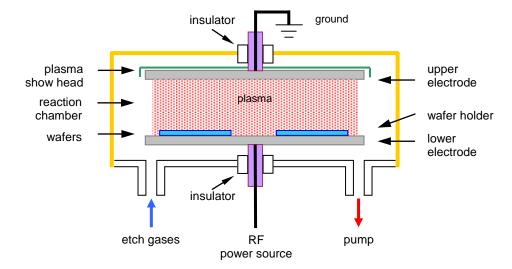

The two most important CVD technologies are *Low Pressure CVD* (LPCVD) and *Plasma Enhanced CVD* (PECVD). The key features are:

- The LPCVD process produces layers with uniformity of thickness and material characteristics. The main processing problems are the high deposition temperature, greater than 600°C, and the relatively slow deposition rate. The PECVD process can operate at lower temperatures, down to 300° C, due to the extra energy supplied to the gas molecules by the ionised vapour precursor, or plasma in the reactor. However, the quality of the films tend to be inferior to processes running at higher temperatures. PECVD relies on electromagnetic means (electric current, microwave excitation), rather than a chemical reaction, to produce a plasma, as in figure 1.10.

- 2. Most PECVD deposition systems can only deposit the material on one side of the wafers, on 1 to 4 wafers at a time. LPCVD systems deposit films on both sides of at least 25 wafers, simultaneously. A schematic diagram of a typical LPCVD reactor is shown in figure 1.11. PECVD films are conformal and deposited at lower temperatures than for LPCVD, although the film is not stoichiometric, prone to cracking and peeling, with by-products formed.

Figure 1.10. Typical PECVD reactor.

CVD is accomplished by placing the substrate wafers in a reactor chamber and heating them to a specific temperature. Controlled amounts of silicon or nitride source gases, usually carried by either nitrogen and/or hydrogen, are added to the reactor. Dopant gases may also be added if desired. A reaction between the source gases and the wafer occurs, thereby depositing the desired layer. Reaction temperatures between 500 to  $1100^{\circ}$ C and pressures ranging from atmospheric to low pressure are used, depending on the specific deposition performed. Heating is usually accomplished with radio frequency, infrared or thermal resistance heating. Common source gases include silane SiH<sub>4</sub>, silicon tetrachloride SiCl<sub>4</sub>, ammonia NH<sub>3</sub>, and nitrous oxide N<sub>2</sub>O. Some dopant gases that are used include arsine AsH<sub>3</sub>, phosphine PH<sub>3</sub>, and diborane B<sub>2</sub>H<sub>6</sub>. The major categories of silicon CVD are shown by the following equations.

#### LPCVD Atmospheric or low pressure

| Medium temperature (600°C to 1100°C)<br>Silicon Nitride, Si <sub>3</sub> N <sub>4</sub> :<br>3 SiH <sub>4</sub> + 4 NH <sub>3</sub> $\rightarrow$ Si <sub>3</sub> N <sub>4</sub> + 12 H <sub>2</sub>                                                                                                               | H <sub>2</sub> carrier gas (900°C to 1100°C)                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Poly Silicon, Poly-Si, $H_2$ carrier gas (850 to 1000°C),<br>SiH <sub>4</sub> + Heat $\rightarrow$ Si + 2 H <sub>2</sub>                                                                                                                                                                                           | N <sub>2</sub> carrier gas (600°C to 700°C)                                                                     |

| Silicon Dioxide, Si0 <sub>2</sub> :<br>SiH <sub>4</sub> + 4 CO <sub>2</sub> $\rightarrow$ SiO <sub>2</sub> + 4 CO + 2 H <sub>2</sub> O<br>2 H <sub>2</sub> + SiCl <sub>4</sub> + CO <sub>2</sub> $\rightarrow$ SiO <sub>2</sub> + 4 HCl<br>SiH <sub>4</sub> + CO $\rightarrow$ SiO <sub>2</sub> + 2 H <sub>2</sub> | $N_2$ carrier gas (500°C to 900°C)<br>$H_2$ carrier gas (800°C to 1000°C)<br>$H_2$ carrier gas (600°C to 900°C) |

| Low Temperature (< 600°C)<br>Silicon Dioxide, Si0 <sub>2</sub> or p-doped Si0 <sub>2</sub> ,<br>SiH <sub>4</sub> + 2 0 <sub>2</sub> + Dopant $\rightarrow$ Si0 <sub>2</sub> + 2 H <sub>2</sub> 0                                                                                                                   | N <sub>2</sub> carrier gas (< 600°C)                                                                            |

| Silicon Nitride, Si <sub>3</sub> N <sub>4</sub> ,<br>3 SiH <sub>4</sub> + 4 NH <sub>3</sub> $\rightarrow$ Si <sub>3</sub> N <sub>4</sub> + 12 H <sub>2</sub><br>3 SiH <sub>4</sub> + 2 N <sub>2</sub> O $\rightarrow$ Si <sub>3</sub> N <sub>4</sub> + 4 H <sub>2</sub> + 2 H <sub>2</sub> O                       | $N_2$ carrier gas (600°C to 700°C)                                                                              |

PECVD Low Temperature Plasma Enhance (passivation) (< 600°C), RF or reactive sputtering

$\begin{array}{ll} \mbox{Silicon Dioxide, Si0}_2: \\ \mbox{SiH}_4 + 2 \ 0_2 \rightarrow Si0_2 + 2 \ H_20 \end{array} & SiH_4 + 0_2 \rightarrow Si0_2 + 2 \ H_2 \end{array}$

Silicon Nitride,  $Si_3N_4$ : 3 SiH<sub>4</sub> + 4 NH<sub>3</sub>  $\rightarrow$  Si<sub>3</sub>N<sub>4</sub> + 12 H<sub>2</sub> 3 SiH<sub>4</sub> + 2 N<sub>2</sub>0  $\rightarrow$  Si<sub>3</sub>N<sub>4</sub> + 4 H<sub>2</sub> + 2 H<sub>2</sub>0

Figure 1.11. Typical horizontal hot-wall LPCVD reactor.

# 1.2.2 Physical Vapour Deposition (PVD)

Physical deposition uses mechanical or thermodynamic means to produce a thin film of solid. Physical deposition covers a number of deposition technologies in which material is released from a source and transferred to the substrate. Physical deposition coatings involve atom-by-atom, molecule-by-molecule or

ion deposition of various materials on solid substrates in vacuum systems. Since most engineering materials bonded together by relatively high energies, and chemical reactions are not used to store these energies, physical deposition systems tend to require a low-pressure vapour environment to function properly.

The material to be deposited is placed in an energetic, entropic environment, so that particles of material escape its surface. Adjacent to this source is a cooler facing surface which draws energy from these particles as they arrive, allowing them to form a solid layer. The system process is in a vacuum deposition chamber, to allow the particles to travel unhindered. Since particles tend to follow a straight trajectory, films deposited by physical means are commonly directional, rather than conformal.

PVD comprises the standard technologies for deposition of metals. It is more common than CVD for metals since it can be performed with lower process risk and cheaper materials costs. The film quality is inferior to CVD, which for metals means higher resistivity and for insulators more defects and traps. The step coverage is also not as good as with CVD.

The choice of deposition method (specifically evaporation versus sputtering) may be arbitrary, and may depend more on what technology is available for the specific material.

Physical deposition includes:

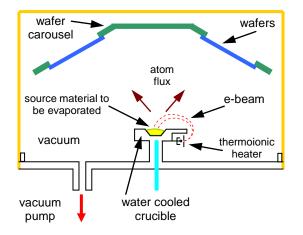

• A thermal evaporator uses an electric resistance heater to melt the material and raise its vapour pressure to a useful range, where it starts to boil and evaporate. An atomic cloud is formed by the evaporation of the coating metal in a vacuum environment to coat all the surfaces in the line of sight between the substrate and the facing target (source). The vacuum allows the vapour to reach the substrate without reacting with or scattering against other gas-phase atoms in the chamber, and reduces the absorption of impurities from the residual gas in the vacuum chamber. Only materials with a higher vapour pressure than the heating element can be deposited without contamination of the film. The method is often used in producing thin, ½ µm, decorative shiny coatings on plastic parts. The thin coating, however, is fragile and wears poorly. The thermal evaporation process can also coat a thick, 1 mm, layer of heat-resistant materials, such as MCrAłY - a metal, chromium, aluminium, and yttrium alloy, on jet engine parts. Molecular beam epitaxy is a particular sophisticated form of thermal evaporation. A schematic diagram of a typical system for e-beam evaporation is shown in figure 1.12.

Figure 1.12. Typical system for e-beam evaporation of materials.

The principle is the same for all evaporation technologies, only the method used to the heat (evaporate) the source material differs. There are two main evaporation technologies, namely e-beam evaporation and resistive evaporation, each referring to the heating method.

- An electron beam evaporator fires a high-energy beam from an electron gun to boil a small spot of material; since the heating is not uniform but local, lower vapour pressure materials can be deposited. The beam is usually bent through a 270° angle in order to ensure that the gun filament is not directly exposed to the evaporant flux. Typical deposition rates for electron beam evaporation range from 1 to 10 nm/s.

- In resistive evaporation, a tungsten boat, containing the source material, is heated electrically with a high current to make the material evaporate. Many materials are restrictive in terms of what evaporation method can be used (that is, aluminium is quite difficult to evaporate using resistive heating), which typically relates to the phase transition properties of that material.

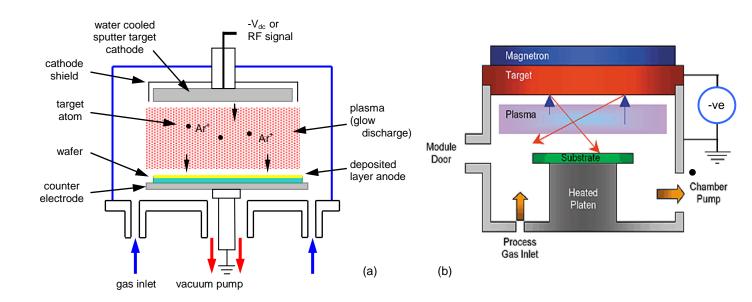

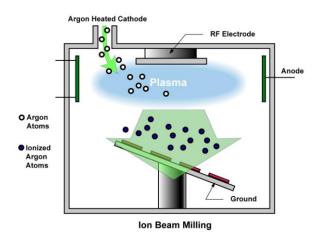

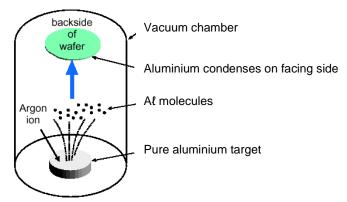

- Sputtering relies on a plasma (usually a noble gas, such as Argon) to knock material from a target or source, a few atoms at a time, at a much lower temperature than with evaporation. The coatings, such as ceramics, metal alloys, organic and inorganic compounds, involve connecting the work-piece and the substance to a high-voltage dc power supply in an argon-vacuum system at 10<sup>-2</sup> to 10<sup>-3</sup> mmHg. The gas plasma is established between the substrate (work-piece) and the target (donor) and transposes the sputtered-off target ionised atoms to the surface of the substrate. Because the target is kept at a relatively low temperature, unlike evaporation, this is a flexible deposition technique. It is especially useful for compounds or mixtures, where different components would otherwise tend to evaporate at different rates. Sputtering's step coverage is virtually conformal, producing thin, less than 3 µm, hard thin-film coatings; for example, titanium nitride (TiN) which is harder than the hardest metal. Sputtering is applied on cutting tools, injection moulding tools, and common tools such as punches and dies, to increase wear resistance and service life. When the substrate is non-conductive, for example, a polymer, radio-frequency (RF) sputtering is used. A schematic diagram of a typical RF sputtering system is shown in figure 1.13a. As for evaporation, the same basic principle applies to all sputtering technologies. The differences typically relate to the manner in which the ion bombardment of the target is realized. Magnetron splutter disposition, figure 1.13b, is used to deposit Al, titanium, and tungsten, although CVD is difficult for alloys, Al-Cu-Si.

- Pulsed laser deposition systems work by an ablation process. Pulses of focused laser light vaporize

the surface of the target material and convert it to plasma; this plasma usually reverts to a gas before

it reaches the substrate.

- Cathodic Arc Deposition or Arc-PVD is a kind of ion beam deposition where an electrical arc is created that blasts ions from the cathode. The arc has a high power density resulting in a high level of ionization (30 to 100%), multiply charged ions, neutral particles, clusters, and macro-particles (droplets). If a reactive gas is introduced during the evaporation process, dissociation, ionization, and excitation occur during interaction with the ion flux and a compound film is deposited.

Figure 1.13. Typical sputtering systems: (a) RF (ac) plasma and (b) dc plasma magnetron.

# Thermal oxidation and the masking process

1.3

The oxide of silicon, silica, or *silicon dioxide* (Si0<sub>2</sub>), is an important planar processing ingredient and a extensively used dielectric in semiconductor manufacturing because it facilitates stable insulation and conformal passivation layers, with a high electric field breakdown strength of 10MV/cm, a resistivity of up to  $10^{20} \Omega$ cm, and a 9eV energy band gap. It is a useful and convenient deposition process, used many times on the silicon wafer surface during device fabrication. Besides the passivation and glass layer deposited over the surface of the die to protect it from mechanical damage and corrosion, dielectric layers are also used for isolating components or structures in the active circuit from each other, and as dielectric structures for MOS transistors and capacitors. Silicon dioxide is used as an insulating barrier between the gate metal and channel of insulated gate semiconductor power switching devices.

The formation of  $SiO_2$  on a silicon surface is accomplished through a process called thermal oxidation, which is a technique that uses high temperatures, usually between 700°C to 1300°C, to promote the growth rate of oxide layers. The thermal oxidation of  $SiO_2$  consists of exposing the silicon substrate to a rich oxidizing atmosphere of oxidisers,  $O_2$  or  $H_2O$ , at elevated temperature, producing oxide films with thicknesses ranging from 6nm to 1µm. Oxidation of silicon is not difficult, since silicon naturally tends to form a stable oxide even at room temperature, provided an oxidizing environment is present. The elevated temperature used in thermal oxidation accelerates the oxidation process, resulting in thicker oxide layers per unit of time. This process affords thickness and property control of the  $SiO_2$  layer.

The silicon wafers placed in a furnace containing oxygen gas for three to four hours at 1000°C to 1200°C, form a surface oxide layer of Si0<sub>2</sub>, usually less than 1µm thick. Wet oxidation, with water added, is about 20 times faster (100nm to 120nm per hour) than dry oxidation (14nm to 25nm per hour) but the oxide quality is lower. The wafer is effectively encapsulated by silica glass, which prevents penetration by impurity atoms, except gallium atoms. Selective diffusions or implanting are made in the silicon by opening windows through the oxide by selective etching with hydrofluoric HF acid following a photo-resist lithography masking process - see section 1.5.

The oxidation furnace (or diffusion furnace, since oxidation is a diffusion process involving oxidant species), provides the heat needed to elevate the oxidizing temperature and the typical furnace consists of:

- a heating system;

- a temperature measurement and control system;

- fused quartz process tubes where the wafers undergo oxidation;

- a system for moving process gases into and out of the process tubes; and

- a loading station used for loading (or unloading) wafers into (or from) the process tubes.

The heating system consists of several heating coils that control the temperature around the furnace tubes. The wafers are placed in quartz glassware called boats, which are supported by fused silica paddles inside the process tube. A boat can contain many wafers, typically 50 or more. The oxidizing agent (oxygen or steam) then enters the process tube through its source end, subsequently diffusing to the wafers where the oxidation occurs. A schematic diagram of a typical wafer oxidation furnace is shown in figure 1.14.

Figure 1.14. Typical wafer oxidation furnace.

Depending on the oxidant species used, namely  $0_2$  or  $H_20$ , the thermal oxidation of Si $0_2$  may either be in the form of dry oxidation, wherein the oxidant is  $0_2$  or wet oxidation, wherein the oxidant is  $H_20$ . The reactions for dry and wet oxidation are characterised by:

In *dry oxidation*, where the oxidising agent is oxygen, 0<sub>2</sub>:

$$Si_{(s)} + O_{2(g)} \rightarrow SiO_{2(s)}$$

(1.27)

During dry oxidation, the silicon wafer reacts with the ambient oxygen (and hydrogen chloride at near atmospheric pressure), forming a layer of silicon dioxide on its surface, usually less than 100nm thick.

In wet oxidation, used for thick oxides, where the oxidising agent is water vapour, H<sub>2</sub>0:

$$Si_{(s)} + 2H_2O_{(g)} \rightarrow SiO_{2(s)} + 2H_{2(g)}$$

(1.28)

Hydrogen and oxygen gases are introduced into a torch chamber where they react to form water molecules, which are then made to enter the reactor under high pressure where they diffuse toward the wafers. The water molecules react with the silicon to produce the oxide and hydrogen gas byproduct.

The oxidation reactions occur at the Si-Si0<sub>2</sub> interface, that is, silicon at the interface is consumed as oxidation takes place. As the oxide grows, the Si-Si0<sub>2</sub> interface moves into the silicon substrate. Consequently, the Si-Si0<sub>2</sub> interface will always be below the original Si wafer surface. Si0<sub>2</sub> formation therefore proceeds in two directions relative to the original wafer surface. Oxidation is the only deposition technology which actually consumes some of the substrate as it proceeds. The amount of silicon consumed by silicon dioxide formation is predictable from the relative densities and molecular weights of Si and Si0<sub>2</sub>. The thickness of silicon consumed is 44% of the final thickness of the oxide formed, thus an oxide that is 100nm thick will consume about 44nm of silicon from the substrate.

Oxidation processes that have short durations (and during the first 50nm of oxide growth), may be modelled by a Linear Growth Law equation:  $x_o = Cx(t + \tau)$ , where  $x_o$  is the growing oxide thickness, *C* is the linear rate constant, *t* is the oxidation time, and  $\tau$  is the initial time displacement to account for the initial oxide layer in situ at the start of the oxidation process. As the process proceeds the oxide growth rate decreases.

For oxidation processes that have long durations (where the oxide thickness reaches 100nm), the rate of oxide formation may be modelled by a Parabolic Growth Law equation:  $x_o^2 = Bxt$ , where  $x_o$  is the growing oxide thickness, *B* is the parabolic rate constant, and *t* is the oxidation time. This equation shows that the oxide thickness grown is proportional to the square root of the oxidizing time, which confirms that oxide growth is hampered as the oxide thickness increases. This is because the oxidizing species diffusion rate decreases as it has to travel a greater distance through the oxide to the Si-Si0<sub>2</sub> interface as the oxide layer thicknes.

Together the linear and parabolic growth equations are known as the Linear-Parabolic Model. This oxide growth model is accurate over a wide temperature range (700°C to 1,300°C), oxide thicknesses (20nm to 2 $\mu$ m), and oxidant partial pressures (0.2 to 2.5 atmospheres). An increase in pressure increases the oxide growth rate, but importantly, allows the temperature to be decreased for a given growth rate. For every 10 atmospheres of pressure, the temperature can be reduced by 30°C.

Oxide growth is accelerated by an increase in oxidation time, oxidation temperature or oxidation pressure. Other factors that affect thermal oxidation growth rate for SiO<sub>2</sub> include:

- the crystallographic orientation of the wafer;

- the wafer's doping level;

- the presence of halogen impurities in the gas phase;

- the presence of plasma during growth; and

- the presence of a photon flux during growth.

Uses for dielectric layers include:

- masking for diffusion and ion implant processes;

- diffusion from doped oxides;

- overcoating of doped films to prevent dopant loss and migration;

- gettering of impurities (see section 1.12); and

- mechanical and chemical protection.

There are other commonly-used dielectric and isolation materials besides Si0<sub>2</sub>.

Silicon dioxide doped with phosphorus (commonly referred to as P-glass, phospho-silicate glass or PSG) is used because it inhibits sodium impurity diffusion and exhibits a smooth topography. Adding boron to PSG results in boro-phospho-silicate glass. BPSG, flows at lower temperatures than PSG; 850°C to 950°C for BPSG as opposed to 950°C to1100°C for PSG.

Polysilicon  $SiO_2$  with enough oxygen content is also semi-insulating and is used in circuit and surface junction passivation. Alternately, silicon nitride is an excellent moisture barrier while stoichiometric silicon nitride is used in oxidation masks and for MOS gate dielectric. These dielectric layers are deposited by sputtering or chemical vapour deposition (CVD). The layer material deposited depends on the processing reactants.

The oxidising process is restricted to materials that can be oxidized, and only films that are oxides or nitrides of that material are possible. Silicon nitride, like silicon dioxide, is an amorphous insulating material that is an excellent moisture and contamination barrier, highly resistant to diffusion, not prone to delamination or cracking, and forms a progressive conformal layer on silicon. The oxidant is pure ammonia gas NH<sub>3</sub> or an ammonia plasma. Although superior to silicon dioxide, it has a much higher dielectric constant 7.5 as opposed to 3.85 for silicon dioxide, so is not favoured for power device insulated gate oxide structures. The disadvantages of silicon nitride are thermal related, namely higher processing temperatures are needed (950 to  $1200^{\circ}$ C) and the thermal expansion of silicon nitride is twice that of silicon dioxide. The relative properties of silicon dioxide, Si<sub>2</sub>, and silicon nitride, Si<sub>3</sub>N<sub>4</sub>, at 300K, are shown in Table 1.3.

LPCVD

$$3SiCl_2H_{2(g)} + 4NH_{3(g)} \rightarrow Si_3N_{4(s)} + 6H_{2(g)}$$

| Properties                                                     |                        | Si0 <sub>2</sub>                    | Si <sub>3</sub> N <sub>4</sub> |  |