# CHAPTER 17

# DC to AC Inverters – Switched Mode

Inversion is the conversion of dc power to ac power at a desired output voltage or current and frequency. A static semiconductor inverter circuit performs this electrical energy inverting transformation. The terms voltage-fed and current-fed are used in connection with the output from inverter circuits.

A *voltage-source inverter* (VSI) is one in which the dc input voltage is essentially constant and independent of the load current drawn. The inverter specifies the load voltage while the drawn current shape is dictated by the load. Being a voltage source, an open circuit output is allowable.

A *current-source inverter* (CSI) is one in which the source, hence the load current is predetermined and the load impedance determines the output voltage. The supply current cannot change quickly. This current is controlled by series dc supply inductance which prevents sudden changes in current. The load current magnitude is controlled by varying the input dc voltage to the large inductance, hence inverter response to load changes is slow. Being a current source, the inverter can survive an output short circuit thereby offering fault ride-through properties, but an open circuit output is problematic.

In the case of a VSI, voltage control may be required to maintain a fixed output voltage when the dc input voltage regulation is poor, or to control load power. The inverter output can be single-phase, three-phase or multi-phase. Variable output frequency may be required for ac motor speed control where, in conjunction with voltage or current control, constant (controlled) motor flux can be maintained.

Inverter output waveforms (either voltage or current) are usually rectilinear in nature and as such contain harmonics which may lead to reduced load efficiency and performance. Load harmonic reduction can be achieved by either filtering, selected harmonic-reduction chopping or pulse-width modulation.

The quality of an inverter output is normally evaluated in terms of its *harmonic factor*,  $\rho$ , *distortion factor*,  $\mu$ , and *total harmonic distortion*, *thd*. In section 15.7.2 these first two factors were defined in terms of the supply current. For VSI inverters the factors are redefined in terms of the output voltage harmonics as follows

$$\rho_n = \left| \frac{V_n}{V_1} \right| = n \mu_n \qquad n > 1 \tag{17.1}$$

The distortion factor for an individual harmonic is

$$\mu_n = \left| \frac{V_n}{n V_1} \right| = \frac{\rho_n}{n} \tag{17.2}$$

$$thd = \sqrt{\left[\sum_{n\geq 2}^{\infty} \left(\frac{V_n}{n}\right)^2\right]} / V_1 = \sqrt{\sum_{n\geq 2}^{\infty} \mu_n^2} = \sqrt{\sum_{n\geq 2}^{\infty} \left(\frac{\rho_n}{n}\right)^2}$$

(17.3)

The factor  $V_n / n$  is used since the harmonic currents produced in an inductive load attenuate with frequency. The harmonic currents produce unwanted heating and torque oscillations in ac motors, although such harmonic currents are not a drawback to the power delivered to a resistive heating load or an incandescent lighting load. Harmonics reflected back into the input may be problematic.

# 17.1 DC-to-ac voltage-source inverter bridge topologies

#### 17.1.1 Single-phase voltage-source inverter bridge

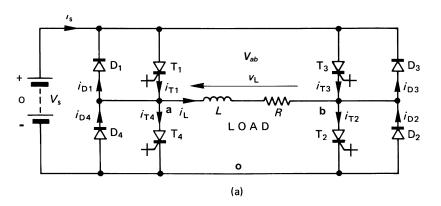

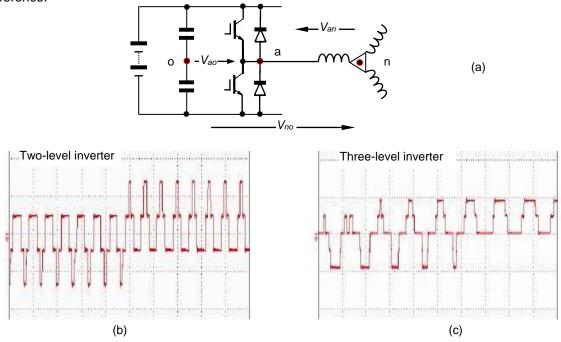

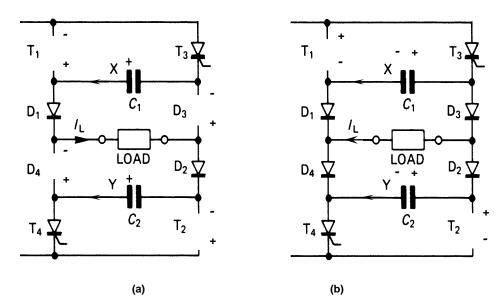

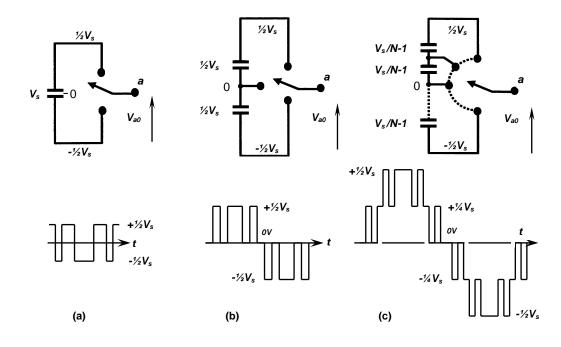

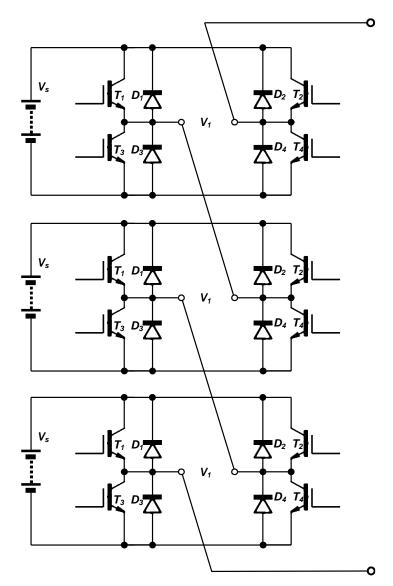

Figure 17.1a shows an H-bridge inverter (VSI) for producing an ac voltage and employing switches which may be transistors (MOSFET or IGBT), or at high powers, thyristors (GTO or GCT). Device

conduction patterns are also shown in figures 17.1b and c. With inductive loads (not purely resistive), stored energy at turn-off is fed through the bridge reactive feedback or freewheel diodes  $D_1$  to  $D_4$ . These four diodes clamp the load voltage to within the dc supply voltage rails (0 to  $V_s$ ).

# 17.1.1i - Square-wave (bipolar) output

Figure 17.1b shows waveforms for a square-wave output  $(2t_1 = t_2)$  where each device is turned on as appropriate for 180°, (that is  $\pi$ ) of the output voltage cycle (state sequence 10, 01, 10, ..). The load current *i*<sub>L</sub> grows exponentially through T<sub>1</sub> and T<sub>2</sub> (state 10) according to

$$V_s = L \frac{di_L}{dt} + i_L R \qquad (V) \tag{17.4}$$

When  $T_1$  and  $T_2$  are turned off,  $T_3$  and  $T_4$  are turned on (state 01), thereby reversing the load voltage polarity. Because of the inductive nature of the load, the load current cannot reverse instantaneously and load reactive energy flows back into the supply via diodes  $D_3$  and  $D_4$  (which are in parallel with  $T_3$  and  $T_4$  respectively) according to

$$-V_s = L \frac{di_L}{dt} + i_L R \qquad (V) \tag{17.5}$$

The load current falls exponentially and at zero,  $T_3$  and  $T_4$  become forward-biased and conduct load current, thereby feeding power to the load.

The output voltage is a square wave of magnitude  $\pm V_s$ , figure 17.1b, and has an rms value of  $V_s$ . For a simple *R-L* load, with time constant  $\tau = L/R$ , during the first cycle with no initial load current, solving equation (17.4) yields a load current

$$i_{L}(t) = \frac{V_{s}}{R} \left( 1 - e^{\frac{-t}{\tau}} \right)$$

(A) (17.6)

Figure 17.1. GCT thyristor single-phase bridge inverter: (a) circuit diagram; (b) square-wave output voltage; and (c) quasi-square-wave output voltage.

#### Power Electronics

Under steady-state load conditions, the initial current is I as shown in figure 17.1b, and equation (17.4) yields

$$i_{L}(t) = \frac{V_{s}}{R} - \left(\frac{V_{s}}{R} - I\right)e^{\frac{-t}{\tau}} \qquad (A)$$

$$0 \le t \le t_{1} = \frac{1}{2}T \qquad (s)$$

for  $v_{L} = V_{s} \qquad (V)$

$$I \le 0 \qquad (A)$$

During the second half-cycle ( $t_1 \le t \le t_2$ ) when the supply is effectively reversed across the load, equation (17.5) yields

$$i_{L}(t) = -\frac{V_{s}}{R} + \left(\frac{V_{s}}{R} + \hat{I}\right)e^{\frac{-t}{\tau}} = -\frac{V_{s}}{R}\left(1 - \left(1 + \tanh\left(\frac{t_{1}}{2\tau}\right)\right)e^{\frac{-t}{\tau}}\right)$$

(A)

$$0 \le t \le t_{2} - t_{1} = \frac{1}{2}T$$

(S)

for  $V_{L} = -V_{s}$ (V)

$$\hat{I} \ge 0$$

(A)

A new time axis has been used in equation (17.8) starting at  $t = t_1$  in figure 17.1b. Since in steady-state by symmetry,  $\hat{I} = -\check{I}$ , the initial steady-state current  $\hat{I}$  can be found from equation (17.7) when, at  $t = t_1$ ,  $i_L = \hat{I}$  yielding

$$\hat{I} = -\check{I} = \frac{V_s}{R} \frac{1 - e^{\frac{-t_1}{\tau}}}{1 + e^{\frac{-t_1}{\tau}}} = \frac{V_s}{R} \tanh\left(\frac{t_1}{2\tau}\right)$$

(A) (17.9)

The zero current cross-over point  $t_x$ , shown on figure 17.1b, can be found by solving equation (17.7) for  $t = t_x$  when  $i_L = 0$ , which yields

$$t_{x} = \tau \, \ell \, n \left( 1 - \frac{\check{I} \, R}{V_{s}} \right)$$

$$= \tau \, \ell \, n \left( 1 + \frac{IR}{V_{s}} \right)$$

(17.10)

The average thyristor current,  $\overline{I}_{\tau}$ , average diode current,  $\overline{I}_{D}$ , and mean source current,  $\overline{I}_{s}$  can be found by integration of the load current over the appropriated bounds shown in the following integrals.

$$\bar{I}_{\tau} = \frac{1}{t_2} \int_{t_x}^{t_1} \dot{r}_{\perp}(t) dt$$

$$= \frac{1}{t_2} \left[ \frac{V_s}{R} (t_1 - t_o) + \tau \left( \frac{V_s}{R} + I \right) \left( e^{\frac{-t_1}{\tau}} - e^{\frac{-t_o}{\tau}} \right) \right]$$

(17.11)

where  $i_{L}$  is given by equation (17.7) and  $\overline{t} = 1 \int_{1}^{t_{x}} i_{x}(t) dt$

$$\bar{I}_{D} = \frac{1}{t_{2}} \int_{0}^{t_{x}} -i_{L}(t) dt$$

$$= \frac{1}{t_{2}} \left[ -\frac{V_{s}}{R} t_{x} - \tau \left( \frac{V_{s}}{R} + I \right) \left( e^{\frac{-t_{x}}{\tau}} - 1 \right) \right]$$

(17.12)

where  $i_{L}$  is given by equation (17.8).

Inspection of the source current waveform in figure 17.1b shows that the average dc voltage source current is related to the average semiconductor device currents by

$$\overline{I}_{s} = 2\left(\overline{I}_{\tau} - \overline{I}_{D}\right)$$

$$= \frac{1}{t_{2}} \left[ \frac{V_{s}}{R} t_{1} + \tau \left( \frac{V_{s}}{R} + I \right) \left( e^{\frac{-t_{1}}{\tau}} - 1 \right) \right]$$

(17.13)

The steady-state mean power delivered by the dc supply and absorbed by the resistive load component R is given by

$$P_{L} = \frac{1}{t_{1}} \int_{0}^{t_{1}} V_{s} i_{L}(t) dt = V_{s} \overline{I}_{s} (= I_{Lrms}^{2} R)$$

(W) (17.14)

where  $i_{L}(t)$  is given by equation (17.7). Rather than integration involving equations (17.7) and (17.8), the mean load power can be used to determine the rms load current:

$$i_{Lrms} = \sqrt{\frac{P_{L}}{R}} = \sqrt{\frac{V_{s}\overline{I_{s}}}{R}}$$

(A) (17.15)

The rms output voltage is  $V_s$  and the output fundamental frequency  $f_o$  is  $f_o = \frac{1}{T} = \frac{1}{2t_1} = \frac{1}{t_2}$ .

The instantaneous output voltage expressed as a Fourier series is given by

$$V_{L} = \frac{4}{\pi} V_{s} \sum_{n \text{ odd}}^{\infty} \frac{1}{n} \sin n \omega_{o} t \qquad (V)$$

(17.16)

where  $\omega_o = 2\pi f_o = 2\pi / t_2 = 2\pi / T$  and for n = 1 the magnitude of the fundament frequency  $f_o$  is  $\frac{4}{\pi}V_s$  which is an output rms fundamental voltage  $v_{o1}$  of

$$V_{o1} = \frac{2\sqrt{2}}{\pi} V_s = 0.90 V_s$$

(V) (17.17)

The load current can be expressed in terms of the Fourier voltage waveform series, that is

$$i_{L}(\omega t) = \frac{4}{\pi} V_{s} \sum_{n=1,3,5}^{\infty} \frac{1}{nZ_{n}} \sin(n\omega_{o}t - \phi_{n})$$

$$= \sum_{n=1,3,5}^{\infty} I_{n} \sin(n\omega_{o}t - \phi_{n})$$

where  $I_{n} = \frac{4}{\pi} \frac{V_{s}}{nZ_{n}}$  whence  $I_{nrms} = \frac{I_{n}}{\sqrt{2}}$

$$Z_{n} = \sqrt{R^{2} + (n\omega_{o}L)^{2}} \qquad \phi_{n} = \tan^{-1} \frac{n\omega_{o}L}{R} \qquad \text{such that} \qquad \cos\phi_{1} = \frac{R}{Z_{1}}$$

The fundamental output power is

$$P_{1} = I_{1}^{2}R = \left(\frac{V_{o1}}{Z_{1}}\right)^{2}R = \frac{V_{s}^{2}}{R}\left(\frac{2\sqrt{2}}{\pi}\right)^{2}\cos^{2}\phi_{1}$$

(17.19)

The load power is given by the sum of each harmonic  $l^2R$  power component, that is

$$P_{L} = \sum_{n=1,3,5}^{\infty} \left( \frac{I_{n}}{\sqrt{2}} \right)^{2} R = \sum_{n=1,3,5}^{\infty} I_{n \ rms}^{2} R \qquad \left( = V_{s} \overline{I}_{s} \right)$$

(17.20)

Alternately, after integrating equation (17.14), with the load current from equation (17.8)

$$P_{L} = \frac{V_{s}^{2}}{R} \left( 1 - \frac{2\tau}{t_{1}} \frac{1 - e^{-\frac{t_{1}}{\tau}}}{1 + e^{-\frac{t_{1}}{\tau}}} \right) = \frac{V_{s}^{2}}{R} \left( 1 - \frac{2\tau}{t_{1}} \tanh\left(\frac{t_{1}}{2\tau}\right) \right)$$

(17.21)

From  $P_L = i_{rms}^2 R$  the rms loads current is

$$i_{Lrms} = \frac{V_s}{R} \sqrt{1 - \frac{2\tau}{t_1} \tanh\left(\frac{t_1}{2\tau}\right)}$$

(17.22)

The load power factor is given by

$$pf = \frac{P}{S} = \frac{i_{Lrms}^2 R}{i_{Lrms} V_{rms}} = \sqrt{1 - \frac{2\tau}{t_1} \tanh\left(\frac{t_1}{2\tau}\right)}$$

(17.23)

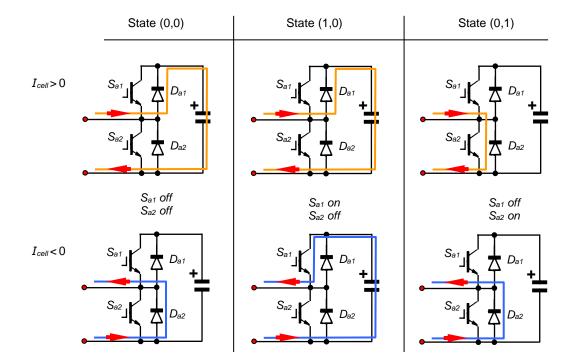

#### 17.1.1ii - Quasi-square-wave (multilevel) output

The rms output voltage form an H-bridge can be varied by producing a quasi-square output voltage ( $2t_1 = t_2$ ,  $t_0 < t_1$ ) as shown in figure 17.1c. After T<sub>1</sub> and T<sub>2</sub> have been turned on (state 10), at the angle  $\alpha$  one device is turned off. (One leg is phase shifted  $\alpha$  relative to the other leg.) If T<sub>1</sub> is turned off (and T<sub>4</sub> is turned on after a short delay), the load current slowly freewheels through T<sub>2</sub> and D<sub>4</sub> (state 00) in a zero voltage loop according to

$$0 = L \frac{di_{L}}{dt} + i_{L}R \qquad (V) \tag{17.24}$$

When  $T_2$  is turned off and  $T_3$  turned on (state 01), the remaining load current rapidly reduces to zero back into the dc supply  $V_s$ , through diodes  $D_3$  and  $D_4$ . When the load current reaches zero,  $T_3$  and  $T_4$  become forward biased and the output current reverses, through  $T_3$  and  $T_4$ .

The output voltage shown in figure 17.1c consists of a sequence of non-zero voltages  $\pm V_s$ , alternated with zero output voltage periods. During the zero output voltage period a diode and switch conduct, firstly T<sub>1</sub> and D<sub>3</sub> in the first period, and T<sub>3</sub> and D<sub>1</sub> in the second zero output period. In each case, a *zero voltage loop* is formed by a switch, diode, and the load. The next two zero output sequences would be T<sub>2</sub> and D<sub>4</sub> then T<sub>4</sub> and D<sub>2</sub>, forming *alternating zero voltage loops* (sequence 10, 00, 01, 11, 10, ...) rather than repeating a continuous T<sub>1</sub> and D<sub>3</sub> then T<sub>3</sub> and D<sub>1</sub> sequence of zero voltage loops (sequence 10, 11, 10, ...)

01, 11, 10, .. or sequence 10, 00, 01, 00, 10, ..). By alternating the zero voltage loops (between states 00 and 11), losses are uniformly distributed between the semiconductors, device switching frequency is half that experienced by the load, and a finer output voltage resolution is achievable.

With reference to figure 17.1c, the load current  $i_L$  for an applied quasi square-wave voltage is defined as follows. (i)  $v_L > 0$

$$i_{L_{T}}(t) = \frac{V_{s}}{R} - \left(\frac{V_{s}}{R} - I_{o}\right)e^{\frac{-t}{\tau}} \qquad 0 \le t \le t_{o} \qquad (17.25)$$

for  $I_{o} \le 0$  (A)

(ii)

$$v_L = 0$$

$i_{L_{II}}(t) = \hat{I} e^{\frac{-t}{r}}$

$0 \le t \le t_1 - t_o$

(17.26)

for

$$\hat{I} \ge 0$$

(A)

(iii)  $v_L < 0$

$i_L(t) = -\frac{V_s}{R} + \left(\frac{V_s}{R} + I_1\right)e^{\frac{-t}{\tau}} = -i_{L_I}(t)$   $0 \le t \le t_o$  (17.27)

for  $I_1 \ge 0$  (A)

The currents  $I_{a}$ ,  $\hat{I}$ , and  $I_{1}$  are given by

$$I_{o} = -\frac{V_{s}}{R} \frac{e^{\frac{-t_{1}+t_{o}}{r}} - e^{\frac{-t_{1}}{r}}}{1 + e^{\frac{-t_{1}}{r}}}$$

(A) (17.28)

$$\hat{I} = \frac{V_s}{R} \frac{1 - e^{-\frac{t_s}{\tau}}}{1 + e^{-\frac{t_1}{\tau}}}$$

(A) (17.29)

$$I_1 = -I_o$$

(A) (17.30)

The zero current cross-over instant,  $t_x$ , shown in figure 17.1c, is found by solving equation (17.25) for t when  $i_L$  equals zero current.

$$t_{x} = \tau \ell n \left( 1 - \frac{I_{o}R}{V_{s}} \right) = \tau \ell n \left( 1 + \frac{I_{1}R}{V_{s}} \right)$$

(17.31)

The average thyristor current,  $\overline{I}_{\tau}$ , average diode current,  $\overline{I}_{D}$ , and mean source current,  $\overline{I}_{s}$  can be found by integration of the load current over the shown bounds (assuming alternating zero volt loops).

$$\overline{I}_{T} = \frac{1}{t_{2}} \int_{t_{x}}^{t_{1}} \dot{I}_{L_{I}}(t) dt + \frac{1}{2t_{2}} \int_{0}^{t_{1}-t_{o}} \dot{I}_{L_{I}}(t) dt$$

(17.32)

where  $i_L$  is given by equations (17.25) and (17.26) for the respective integrals, and

$$\overline{I}_{D} = \frac{1}{t_{2}} \int_{0}^{t_{x}} -i_{L_{I}}(t) dt + \frac{1}{2t_{2}} \int_{0}^{t_{1}-t_{o}} i_{L_{II}}(t) dt$$

(17.33)

where  $i_{L}$  is given by equations (17.25) and (17.26) for the respective integrals.

Inspection of the source current waveform in figure 17.1c shows that the average source current is related to the average semiconductor device currents by

$$\overline{I}_{s} = \frac{1}{t_{1}} \int_{0}^{t_{0}} i_{L_{T}}(t) dt = 2 \left( \overline{I}_{T} - \overline{I}_{D} \right)$$

(17.34)

The steady-state mean load and dc source powers are

$$P_{L} = \frac{1}{t_{1}} \int_{0}^{t_{o}} V_{s} i_{L}(t) dt = V_{s} \overline{I}_{s} \qquad \left(= I_{Lrms}^{2} R\right) \qquad (W)$$

(17.35)

where  $i_{L}(t)$  is given by equation (17.25). The mean load power can be used to determine the rms load current:

$$I_{Lrms} = \sqrt{\frac{P_{L}}{R}} = \sqrt{\frac{V_{s}\overline{I}_{s}}{R}}$$

(A) (17.36)

The output fundamental frequency  $f_o$  is  $f_o = \frac{1}{2t_1} = \frac{1}{t_2}$ .

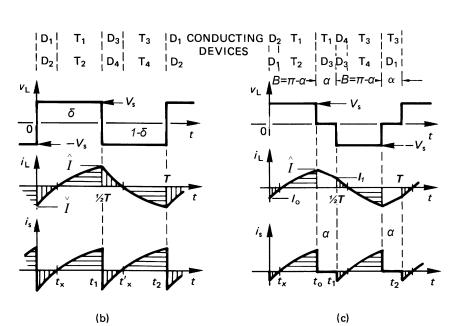

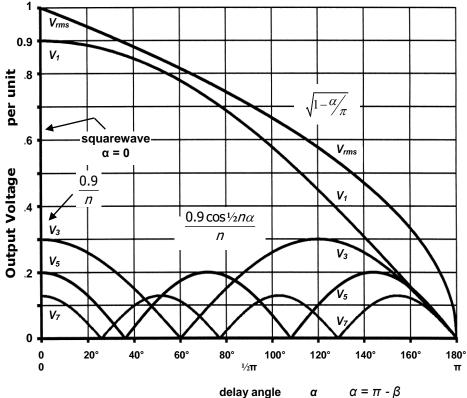

The variable rms output voltage, for  $0 \le \alpha \le \pi$ , is

$$V_{rms} = \sqrt{\frac{1}{t_1} \int_0^{t_0} V_s^2 dt} = \sqrt{1 - \frac{\alpha}{\pi}} V_s$$

(17.37)

and the output fundamental frequency  $f_o$  is  $f_o = \frac{1}{t_2}$ . This equation for rms output voltage shows that only the  $n^{th}$  harmonic can be eliminated when  $\cos \frac{1}{2n\alpha} = 0$ , that is for  $\alpha = \pi / n$ . In so eliminating the  $n^{th}$  harmonic, from equation (17.38), the magnitude of the fundamental is reduced to  $\frac{4}{\pi}V_s \cos \frac{\pi}{n}$ . The output voltage  $V_L$  in its Fourier coefficient series form is given by

$$V_{L} = \frac{4}{\pi} V_{s} \sum_{n \text{ odd}}^{\infty} \frac{\cos \frac{1}{2} n \alpha}{n} \sin n \omega_{o} t \qquad (V)$$

and for n = 1, the rms fundamental of the output voltage  $v_{o1}$  is given by

$$V_{o1} = \frac{2\sqrt{2}}{\pi} V_s \cos \frac{1}{2}\alpha = 0.90 \times V_s \times \cos \frac{1}{2}\alpha \qquad (V)$$

(17.39)

The characteristics of these load voltage harmonics are shown in figure 17.2.

An alternative approach is to consider the control of one leg phase shifted by  $\beta$  radians with respect of the other leg. The phase output voltage for each leg, with respect to the supply (artificial) mid point, o, is

$$V_{ao} = \sum_{n=1,3,5,\dots}^{\infty} \frac{2V_s}{n\pi} \sin n\omega_o t$$

$$V_{bo} = \sum_{n=1,3,5,\dots}^{\infty} \frac{2V_s}{n\pi} \sin(n(\omega_o t - \beta))$$

The output  $V_{ab}$  is then given by the difference, that is

$$V_{ao} - V_{bo} = V_{ab} = \sum_{n=1,3,5,\dots}^{\infty} \frac{2V_s}{n\pi} \sin n\omega_o t - \sum_{n=1,3,5,\dots}^{\infty} \frac{2V_s}{n\pi} \sin(n(\omega_o t - \beta))$$

$$= \sum_{n=1,3,5,\dots}^{\infty} \frac{4V_s}{n\pi} \sin \frac{1}{2}n\beta \cos n\omega_o t$$

Expressing the phase shift angle  $\beta$  in terms of the delay angle  $\alpha$ , where  $\beta = \pi - \alpha$ , yields equation (17.38).

The load current can be expressed in terms of the Fourier voltage waveform series, that is

$$i_{L}(\omega t) = \frac{V_{L}}{Z_{L}} = \frac{4}{\pi} V_{s} \sum_{n=1,3,..}^{\infty} \frac{\cos V_{2} n \alpha}{n Z_{n}} \sin (n \omega_{o} t - \phi_{n}) = \sum_{n=1,3,5,..}^{\infty} I_{n} \sin (n \omega_{o} t - \phi_{n})$$

(17.40)

where  $I_{n} = \frac{4}{\pi} \frac{V_{s}}{n Z_{n}} \cos V_{2} n \alpha$  whence  $I_{n_{\text{rms}}} = \frac{I_{n}}{\sqrt{2}}$

$Z_{n} = \sqrt{R^{2} + (n \omega_{o} L)^{2}} \qquad \phi_{n} = \tan^{-1} \frac{n \omega_{o} L}{R}$

Figure 17.2. Full bridge inverter output voltage harmonics normalised with respect to square wave rms output voltage,  $V_{rms}=V_s$ .

The load power is given by the sum of each harmonic  $l^2R$  power component, that is

$$P_{L} = \sum_{n=1,3,5}^{\infty} \left( \frac{I_{n}}{\sqrt{2}} \right)^{2} R = \sum_{n=1,3,5,\dots}^{\infty} I_{n \ rms}^{2} R \qquad \left( = V_{s} \overline{I}_{s} \right)$$

(17.41)

The load power and rms current can be evaluated from equations (17.21) and (17.22) provided the rms voltage given by equation (17.37) replaces  $V_{s}$ . That is

$$P_{L} = \frac{V_{s}^{2}}{R} \left(1 - \frac{\alpha}{\pi}\right) \left(1 - \frac{2\tau}{t_{1}} \tanh\left(\frac{t_{1}}{2\tau}\right)\right) = I_{Lrms}^{2} R$$

(17.42)

$$i_{Lrms} = \frac{V_s}{R} \sqrt{1 - \alpha/\pi} \sqrt{1 - \frac{2\tau}{t_1}} \tanh\left(\frac{t_1}{2\tau}\right)$$

(17.43)

The load power factor is independent of  $\alpha$  and is given by equation (17.23), that is

$$\rho f = \frac{P}{S} = \frac{i_{Lrms}^2 R}{i_{Lrms} V_{rms}} = \sqrt{1 - \frac{2\tau}{t_1}} \tanh\left(\frac{t_1}{2\tau}\right)$$

(17.44)

A variation of the basic four-switch dc to ac single-phase H-bridge is the half-bridge version where two series switches (one pole or leg) and diodes are replaced by a split two-capacitor voltage source, as shown in figure 17.3. This reduces the number of semiconductors and gate circuit requirements, but at the expense of halving the maximum output voltage. Example 17.3 illustrates the half-bridge and its essential features. Behaviour characteristics are as for the full-bridge, square-wave, single-phase inverter but  $V_s$  is replaced by  $\frac{1}{2}V_s$  in the appropriate equations. Only a rectangular-wave bipolar output voltage can be obtained. Since zero volt loops cannot be created, no rms voltage control is possible. The rms output voltage is  $\frac{1}{2}V_s$ , while the output power is a quarter that of the full H-bridge.

# Example 17.1: Single-phase H-bridge with an L-R load

A single-phase H-bridge inverter, as shown in figure 17.1a, supplies a 10  $\Omega$  resistance with inductance 50 mH, from a 340 V dc source. If the bridge is operating at 50 Hz (output), determine the average supply current and the load rms voltage and current and steady-state current waveforms with

- *i.* a square-wave output

- *ii.* a symmetrical quasi-square-wave output with a 50 per cent on-time.

#### Solution

The time constant of the load,  $\tau = 0.05$ mH/10 $\Omega = 5$  ms,  $t_1 = 10$ ms and  $t_2 = 20$ ms.

*i.* The output voltage rms value is 340 V ac.

Equation (17.9) gives the load current at the time when the supply polarity is reversed across the load, as shown in figure 17.1b, that is

$$\hat{I} = -\check{I} = \frac{V_s}{R} \frac{1 - e^{\frac{v}{r}}}{1 + e^{\frac{-t_1}{r}}}$$

(A)

where  $t_1 = 10$  ms. Therefore

$$\hat{I} = -\hat{I} = \frac{340V}{10\Omega} \times \frac{1 - e^{-2}}{1 + e^{-2}}$$

(A)

= 25.9A

When  $v_L = +340$  V, from equation (17.7) the load current is given by

$i_{L} = 34 - (34 + 25.9) \times e^{-200t} = 34 - 59.9e^{-200t}$   $0 \le t \le 10 \text{ ms}$

From equation (17.10) the zero current cross-over time,  $t_x$ , occurs  $5\text{ms} \times \ell n (1 + 25.9\text{A} \times 10\Omega/340\text{V}) = 2.83\text{ms}$  after load voltage reversal.

When

$$v_L = -340$$

V, from equation (17.8) the load current is given by

$i_t = -34 + (34 + 25.9) \times e^{-200t} = -34 + 59.9e^{-200t}$   $0 \le t \le 10$  ms

The mean power delivered to the load is given by equation (17.14), that is

$$P_{L} = \frac{1}{10 \text{ms}} \int_{0}^{10 \text{ms}} 340 \text{V} \times \{34 - 59.9 \times e^{-200t}\} dt$$

= 2755 W

From  $P = i^2 R$ , the load rms current is

$$i_{Lms} = \sqrt{\frac{P_L}{R}} = \sqrt{\frac{2755W}{10\Omega}} = 16.60A$$

and  $\overline{I}_s = \frac{\frac{P_L}{V_s}}{\frac{2755W}{340V}} = 8.1A$

These power and rms current results can be confirmed with equations (17.21) and (17.22).

- 718

- *ii.* The quasi-square output voltage has a 5 ms on-time, *t*<sub>o</sub>, and a 5 ms period of zero volts.

From equation (17.37) the rms output voltage is  $V_s \sqrt{1-5\text{ms}/10\text{ms}} = \frac{V_s}{\sqrt{2}} = 240\text{V rms}.$

The current during the different intervals is specified by equations (17.25) to (17.30). Alternately, the steady-state load current equations can be specified by determining the load current equations for the first few cycles at start-up until steady-state conditions are attained.

First 5 ms on-period when  $v_L = 340$  V and initially  $i_L = 0$  A  $i_{i} = 34 - 34 e^{-200t}$ and at 5ms,  $i_L = 21.5A$ First 5 ms zero-period when  $v_L = 0$  V  $i_{L} = 21.5 \ e^{-200t}$ and at 5ms,  $i_{L}$  =7.9A Second 5 ms on-period when  $v_L = -340$  V  $i_{L} = -34 + (34 + 7.9) \times e^{-200t}$ with  $i_L = 0$  at 1 ms and ending with  $i_L = -18.6$  A Second 5 ms zero-period when  $v_L = 0$  V  $i_{i}$  = -18.6  $e^{-200t}$ ending with  $i_L = -6.8A$ Third 5 ms on-period when  $v_L = 340$  V  $i_{L} = 34 - (34 + 6.8) \times e^{-200t}$ with  $i_L = 0$  at 0.9 ms and ending with  $i_L = 19.0$  A Third 5 ms zero-period when  $v_L = 0$  V  $i_{l} = 19.0 e^{-200t}$ ending with  $i_{L} = 7.0A$ Fourth 5 ms on-period when  $v_L = -340$  V  $i_{l} = -34 + (34 + 7.0) \times e^{-200t}$ with  $i_L = 0$  at 0.93 ms and ending with  $i_L = -18.9$  A Fourth 5 ms zero-period when  $v_L = 0$  V  $i_{L}$  = -18.9  $e^{-200t}$ ending with  $i_L = -7.0A$

Steady-state load current conditions have been reached and the load current waveform is as shown in figure 17.1c. Convergence of an iterative solution is more rapid if the periods considered are much longer than the load time constant (and vice versa).

The mean load power for the quasi-square wave is given by

$$P_{L} = \frac{1}{10 \text{ms}} \int_{0}^{5 \text{ms}} 340 \text{V} \times \{34 - 41 \times e^{-200t}\} dt$$

= 1378 W

The load rms and supply currents are

$$i_{Lms} = \sqrt{\frac{P_L}{R}} = \sqrt{\frac{1378W}{10\Omega}} = 11.74A$$

$\overline{I}_s = \frac{\frac{P_L}{V_s}}{1378W} = 1378W_{340V} = 4.05A$

# Example 17.2: H-bridge inverter ac output factors

In each waveform case (square and quasi-square) of example 17.1a calculate

- *i.* the average and peak current in the switches

- *ii.* the average and peak current in the diodes

- iii. the peak blocking voltage of each semiconductor type

- *iv.* the average source current

- v. the harmonic factor and distortion factor of the lowest order harmonic

- *vi.* the total harmonic distortion

# Solution

# Square-wave

*i*. The peak current in the switch is  $\hat{I} = 25.9$  A and the current zero cross-over occurs at  $t_x = 2.83$ ms. The average switch current, from equation (17.11) is

$$\overline{I}_{T} = \frac{1}{20 \text{ms}} \int_{2.83 \text{ms}}^{10 \text{ms}} 34 - 59.9 \ e^{-200t} \ dt$$

$$= 5.71 \ \text{A}$$

ii. The peak diode current is 25.9 A. The average diode current from equation (17.12) is

$$\overline{I}_{D} = \frac{1}{20 \text{ms}} \int_{0}^{2.83 \text{ms}} (34 - 59.9 \ e^{-200t}) \ dt$$

$$= 1.66 \text{ A}$$

- iii. The maximum blocking voltage of each device is 340 V dc.

- iv. The average supply current is

$$\overline{I}_{s} = 2\left(\overline{I}_{T} - \overline{I}_{D}\right) = 2 \times (5.71 \text{A} - 1.66 \text{A}) = 8.10 \text{A}$$

This results in the supply delivery power of 340 Vdc × 8.10A = 2754W

v. From equation (17.16), with the third as the lowest harmonic, the distortion factors are

$$hf = \rho_3 = \left| \frac{V_3}{V_1} \right| = \frac{1}{3}, \text{ that is, } 33\frac{1}{3} \text{ per cent}$$

$$df = \mu_3 = \left| \frac{V_3}{3V_1} \right| = \frac{1}{9}, \text{ that is, } 11.11 \text{ per cent}$$

vi. From equation (17.16)

thd =

$$\sqrt{\sum \left(\frac{V_n}{n}\right)^2 / V_1}$$

=  $\sqrt{\left(\frac{1}{3}\right)^2 + \left(\frac{1}{5}\right)^2 + \left(\frac{1}{7}\right)^2 + \dots}$

= 46.2 per cent

**Quasi-square-wave**,  $\alpha = \frac{1}{2}\pi$  (5 ms) and from equation (17.31)  $t_x = 0.93$ ms

*i.* The peak switch current is 18.9 A.

From equation (17.32) the average switch current, using alternating zero volt loops, is

$$\overline{I}_{\tau} = \frac{1}{20\text{ms}} \int_{0.93\text{ms}}^{5\text{ms}} (34 - 41e^{-200t}) dt + \frac{1}{40\text{ms}} \int_{0}^{5\text{ms}} 19e^{-200t} dt$$

$$= 2.18 + 1.50 = 3.68 \text{ A}$$

*ii.* The peak diode current (and peak switch current) is 18.9 A. The average diode current, from equation (17.33), when using alternating zero volt loops, is given by

$$\overline{I}_{D} = \frac{1}{20 \text{ms}} \int_{0}^{0.93 \text{ms}} \left(-34 + 41 e^{-200t}\right) dt + \frac{1}{40 \text{ms}} \int_{0}^{5 \text{ms}} 19 e^{-200t} dt$$

$$= 0.16 + 1.50 = 1.66 \text{ A}$$

- iii. The maximum blocking voltage of each device type is 340 V.

- iv. The average supply current is

$$\overline{I}_{s} = 2(\overline{I}_{T} - \overline{I}_{D}) = 2 \times (3.68 \text{A} - 1.66 \text{A}) = 4.04 \text{A}$$

This results in the supply delivery power of 340 Vdc × 4.04A = 1374W

v. The harmonics are given by equations (17.1) to (17.3)

$$hf = \rho_3 = \left| \frac{V_3}{V_1} \right| = \frac{1}{3\sqrt{2}} / \frac{1}{\sqrt{2}} = \frac{1}{3}, \text{ that is, } 33\frac{1}{3} \text{ per cent}$$

$$df = \mu_3 = \left| \frac{V_3}{nV_1} \right| = \frac{\rho_3}{n} = \frac{1}{9}, \text{ that is, } 11.11 \text{ per cent}$$

vi.

thd =

$$\sqrt{\left[\sum_{n\geq 2}^{\infty} \left(\frac{V_n}{n}\right)^2\right]} / V_1$$

=  $\sqrt{\left(\frac{1}{3}\right)^2 + \left(\frac{-1}{5}\right)^2 + \left(\frac{1}{7}\right)^2 + \left(\frac{1}{9}\right)^2 + \dots} = 46.2 \text{ per cent}$

#### Example 17.3: Harmonic analysis of H-bridge inverter with an L-R load

For each delay case ( $\alpha = 0^{\circ}$  and  $\alpha = 90^{\circ}$ ) in example 17.1, using Fourier voltage analysis, determine (ignore harmonics above the 10<sup>th</sup>):

- *i.* the magnitude of the fundamental and first four harmonics

- *ii.* the load rms voltage and current

- iii. load power

- iv. load power factor

#### Solution

| n        | Zn                                       | V <sub>n</sub> (α=0) | I <sub>n</sub> (α=0) | V <sub>n</sub> (α=90°)             | I <sub>n</sub> (α=90°) |

|----------|------------------------------------------|----------------------|----------------------|------------------------------------|------------------------|

| harmonic | $\sqrt{R^2 + \left(2\pi 50 nL\right)^2}$ | $\frac{0.9V_s}{n}$   | $V_n/Z_n$            | $\frac{0.9V_s}{n}\cos(1/2n\alpha)$ | $V_n/Z_n$              |

|          | Ω                                        | v                    | Α                    | V                                  | Α                      |

| 1        | 18.62                                    | 306                  | 16.43                | 216.37                             | 11.62                  |

| 3        | 48.17                                    | 102                  | 2.12                 | -72.12                             | -1.50                  |

| 5        | 79.17                                    | 61.2                 | 0.77                 | -43.28                             | -0.55                  |

| 7        | 110.41                                   | 43.71                | 0.40                 | 30.91                              | 0.28                   |

| 9        | 141.72                                   | 34                   | 0.24                 | 24.04                              | 0.17                   |

|          |                                          | 332.95V              | 16.59A               | 235.43V                            | 11.73A                 |

The appropriate harmonic analysis is outline in the following table, for  $\alpha = 0^{\circ}$  and  $\alpha = 90^{\circ}$ .

*i*. The magnitude of the fundamental voltage is 306V for the square wave and is reduced to 216V when a phase delay angle of 90° is introduced. The table shows that the harmonics magnitudes reduce  $(\frac{1}{n})$  as the harmonic order increases.

*ii.* The rms load current and voltage can be derived by the square root of the sum of the squares of the fundamental and harmonic components, that is, for the current

$$\dot{I}_{rms} = \sqrt{I_1^2 + I_3^2 + I_5^2 + \dots}$$

The load rms currents, from the table, are 16.59A and 11.73A, which agree with the values obtained in example 17.1a. Notice that the predicted rms voltages of 333V and 235V differ significantly from the values in example 17.1a, given by  $V_s\sqrt{1-\frac{\alpha}{\pi}}$ , namely 340V and 240.4V respectively. This is because the magnitude of the harmonics higher in order than 10 are not insignificant. The error introduced into the rms current value by ignoring these higher order voltages is insignificant because the impedance increases approximately proportionally with harmonic number, hence the resultant current becomes much smaller (insignificant) as the order increases.

iii. The load power is the load i<sup>2</sup>R loss, that is

$$P_{L} = i_{ms}^{2} R = 16.59^{2} \times 10\Omega = 2752W \text{ for } \alpha = 0$$

$$P_{L} = i_{ms}^{2} R = 11.73^{2} \times 10\Omega = 1376W \text{ for } \alpha = 90^{\circ}$$

iv. The load power factor is the ratio of real power dissipated to apparent power, that is

$$pf = \frac{P}{S} = \frac{i_{rms}^{2}R}{i_{rms}v_{rms}} = \frac{2752W}{16.59A \times 340V} = 0.488 \text{ for } \alpha = 0$$

$$pf = \frac{P}{S} = \frac{i_{rms}^{2}R}{i_{rms}v_{rms}} = \frac{1376W}{11.79A \times 240.4V} = 0.486 \text{ for } \alpha = 90^{\circ}$$

Equations (17.23) and (17.44) confirm the load power factor is 0.488, independent of  $\alpha$ .

# Example 17.4: Single-phase half-bridge inverter with an L-R load

A single-phase half-bridge inverter as shown in the figure 17.3, supplies a 10  $\Omega$  resistance with inductance 50 mH from a 340 V dc source. If the bridge is operating at 50 Hz, determine for the square-wave output

- *i.* steady-state current waveforms

- ii. the load rms voltage (the capacitors block any dc voltage output component)

- *iii.* the peak load current and its time domain solution,  $i_{L}(t)$

- *iv.* the average and peak current in the switches

- v. the average and peak current in the diodes

- vi. the peak blocking voltage of each semiconductor type

- vii. the power delivered to the load, rms load current, and average supply current

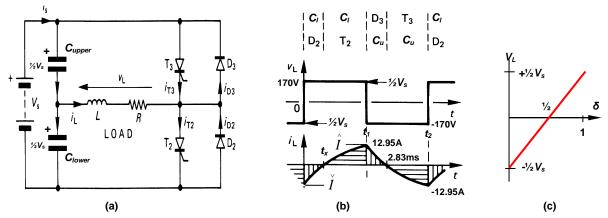

Figure 17.3. GCT thyristor single-phase half-bridge inverter: (a) circuit diagram; (b) square-wave output voltage; and (c) output voltage transfer function.

## Solution

From examples 17.1 and 17.2,  $\tau = 5$ ms.

*i.* Figure 17.3 shows the output voltage and current waveforms, with various circuit component current waveforms superimposed. Note that no zero voltage loops can be created with the half-bridge. Only load voltages  $\pm \frac{1}{2} V_s$ , that is  $\pm 170V$  dc, are possible.

- *ii.* The output voltage swing is  $\pm \frac{1}{2}V_s$ ,  $\pm 170V$ , thus the rms output voltage is  $\frac{1}{2}V_s$ , 170V. This is, half that of the full-bridge inverter using the same magnitude source voltage  $V_s$ , 340V dc.

- iii. The peak load current is half that given by equation (17.9), that is

$$\hat{I} = \frac{\frac{1}{2}V_s}{R} \frac{1 - e^{\frac{-t_1}{\tau}}}{1 + e^{\frac{-t_1}{\tau}}} = \frac{\frac{1}{2}V_s}{R} \tanh\left(\frac{t_1}{2\tau}\right)$$

$$= \frac{\frac{1}{2} \times 340V}{10\Omega} \times \tanh\left(\frac{10ms}{2\times 5ms}\right) = 12.95A$$

The load current waveform is defined by equations (17.7) and (17.8), specifically

$$i_{L_{I}}(t) = \frac{\frac{1}{2}V_{s}}{R} - \left(\frac{\frac{1}{2}V_{s}}{R} - I\right) \times e^{\frac{-t}{r}}$$

$$= \frac{\frac{1}{2} \times 340V}{10\Omega} - \left(\frac{\frac{1}{2} \times 340V}{10\Omega} + 12.95A\right) \times e^{\frac{-t}{5ms}}$$

$$= 17 - 29.95 e^{\frac{-t}{5ms}} \quad \text{for} \quad 0 \le t \le 10\text{ms}$$

and

$$i_{L_{II}}(t) = -\frac{\frac{1}{2}V_s}{R} + \left(\frac{\frac{1}{2}V_s}{R} + \hat{I}\right) \times e^{\frac{-t}{r}}$$

$$= -\frac{\frac{1}{2}\times340V}{10\Omega} + \left(\frac{\frac{1}{2}\times340V}{10\Omega} + 12.95\right) \times e^{\frac{-t}{5ms}}$$

$= -17 + 29.95 e^{\overline{5ms}} \qquad \text{for} \qquad 0 \le t \le 10 \text{ms}$ By halving the effective supply voltage, the current swing is also halved. iv. The peak switch current is I = 12.95A.

The average switch current is given by

$$\overline{I}_{\tau} = \frac{1}{20 \text{ms}} \int_{2.83 \text{ms}}^{10 \text{ms}} (17 - 29.95 e^{\frac{-t}{5 \text{ms}}}) dt$$

$$= 2.86 \text{ A}$$

v. The peak diode current is I = 12.95A. The average diode current is given by

$$\overline{I}_{D} = \frac{1}{20\text{ms}} \int_{0}^{2.83\text{ms}} \left( 17 - 29.95e^{\frac{-t}{5\text{ms}}} \right) dt$$

$$= 0.83 \text{ A}$$

- *vi.* When a switch or diode of a parallel pair conduct, the complementary pair of devices experience a voltage  $V_s$ , 340V dc. Thus although the load experiences half the supply voltage, the semiconductors experience twice that voltage, the same voltage experienced by the switches in the full bridge inverter.

- vii. The load power (whence various currents) is found by averaging the instantaneous load power

$$P_{L} = \frac{1}{10 \text{ms}} \int_{0}^{10 \text{ms}} 170 \text{V} \times (17 - 29.95 \times \text{e}^{-200t}) dt \qquad i_{rms} = \sqrt{\frac{P_{L}}{R}} \qquad \overline{I}_{s} = \frac{\frac{P_{L}}{V_{s}}}{10\Omega} = 8\text{A} \qquad = \frac{638.5 \text{W}}{340 \text{V}} = 1.88\text{A}$$

# 17.1.1iii - PWM-wave output

The output voltage and frequency of a single-phase voltage-source inverter bridge can be control using one of two forms of pulse-width modulation, termed:

- bipolar

- multi-level, usually (meaninglessly) called unipolar

Both pwm techniques have been analysed extensively for dc voltage outputs when applied to the two quadrant and four quadrant dc choppers considered in Chapter 16, sections 16.5 and 16.6. It will be seen that the same triangular modulation principles can be applied and extended, when producing low-harmonic single-phase ac output voltages and currents. The main voltage output difference between the two methods is the harmonic content near the carrier frequency and its harmonics. Three-phase pwm is a naturally extension to the single-phase case, except single-phase pwm offers more degrees of flexibility than its application to three phase inverters, although three-phase pwm does have the attribute of triplen harmonic cancellation, due to the use of one (co-phasal) triangular carrier.

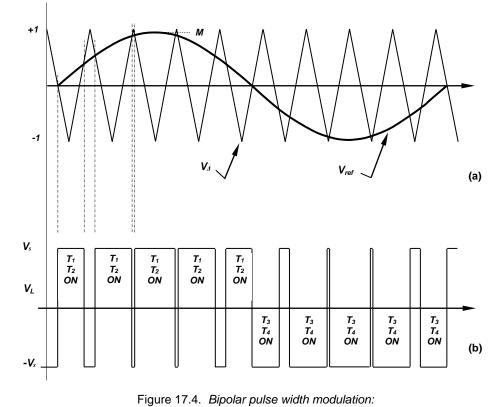

# **Bipolar pulse width modulation**

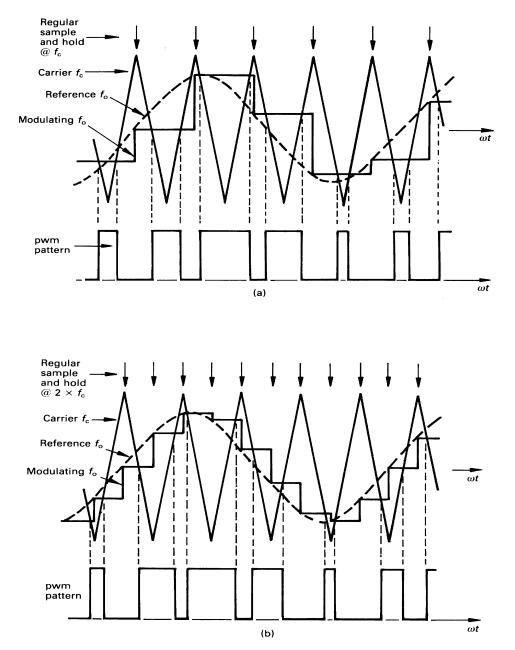

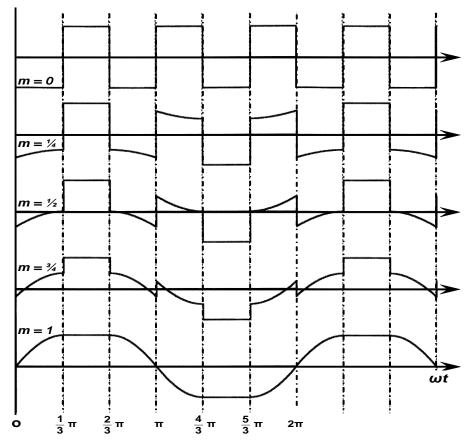

Bipolar modulation is the simplest pwm method and involves comparing a fixed frequency and magnitude triangular carrier with the ac waveform desired, called the modulation waveform. The modulation waveform is usually a sinusoid of magnitude (modulation index) M such that  $0 \le M \le 1$ .

The waveforms in figure 17.4 shown that the load voltage  $V_L$  swings between the two voltage levels,  $+V_s$  and  $-V_s$ , (hence the term bipolar output voltage), according to

- $T_1$  and  $T_2$  are on when  $v_{ref} > v_{\Delta}$  ( $T_3$  and  $T_4$  are off) such that  $V_L = +V_s$

- $T_3$  and  $T_4$  are on when  $v_{ref} < v_{\Delta}$  ( $T_1$  and  $T_2$  are off) such that  $V_L = -V_s$

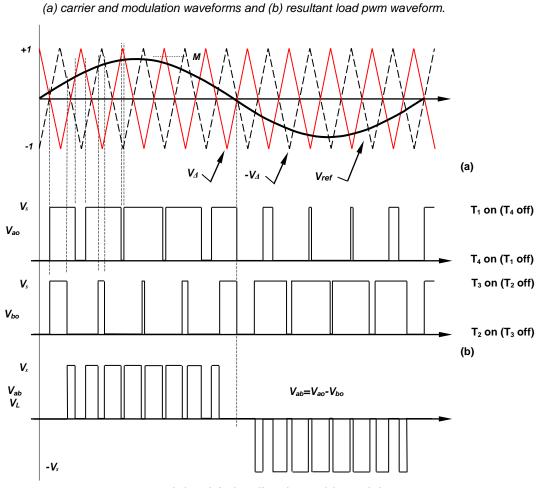

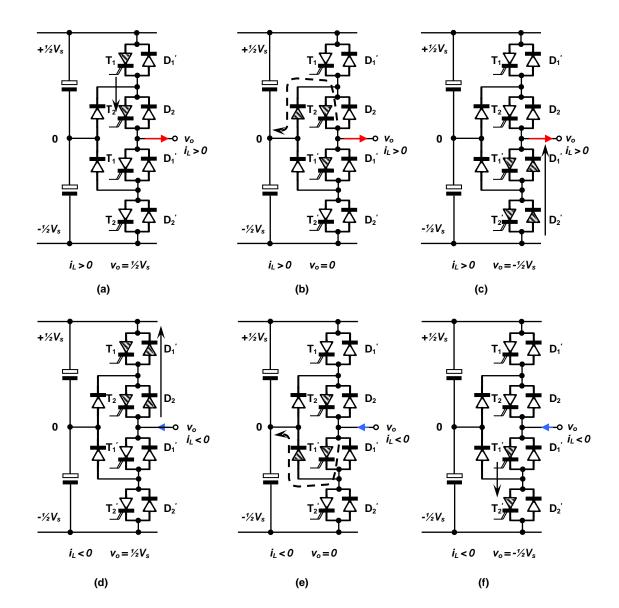

# Multi-level pulse width modulation

Two multilevel output voltage techniques can be use with single-phase voltage fed ac bridges. In both case, two triangular carries displaced by 180° give the same output for the same switching frequency.

- i. The waveforms in figure 17.5 show that the load voltage  $V_L$  swings between the two voltage levels,  $+V_s$  and  $-V_s$ , with interspaced zero periods (hence the term multilevel, specifically three-level in this case, 0V and  $\pm V_s$ ), according to

- $T_1$  is on when  $v_{ref} > v_{\Delta}$  such that  $V_{ao} = +V_s$

- T<sub>4</sub> is on when  $v_{ref} < v_{\Delta}$  such that  $V_{ao} = OV$

- $T_3$  is on when  $v_{ref} < -v_{\Delta}$  such that  $V_{bo} = V_s$

- $T_2$  is on when  $v_{ref} > -v_{\Delta}$  such that  $V_{bo} = OV$

The multilevel load output voltage is the difference between the two leg voltage waveforms and can be defines as follows:

- T<sub>1</sub> and T<sub>2</sub> are on such that  $V_{ao} = +V_s$ ,  $V_{bo} = 0V$ ,  $V_{ab} = +V_s$ T<sub>2</sub> and T<sub>3</sub> are on such that  $V_{ao} = 0V$ ,  $V_{bo} = +V_s$ ,  $V_{ab} = -V_s$ •

- •

- $T_1$  and  $T_3$  are on such that  $V_{ao} = +V_s$ ,  $V_{bo} = +V_s$ ,  $V_{ab} = 0V$

- $T_2$  and  $T_4$  are on such that  $V_{ao} = 0V$ ,  $V_{bo} = 0V$ ,  $V_{ab} = 0V$ •

Figure 17.5. Multilevel (3 level) pulse width modulation: (a) carriers and modulation waveforms and (b) resultant load pwm waveforms.

The two zero output states are interleaved to balance switching losses between all four bridge switches. Device switching is at the carrier frequency, but the bridge load voltage (hence load current) experiences twice the leg switching frequency since the two carriers are displaced by 180°.

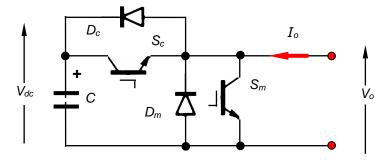

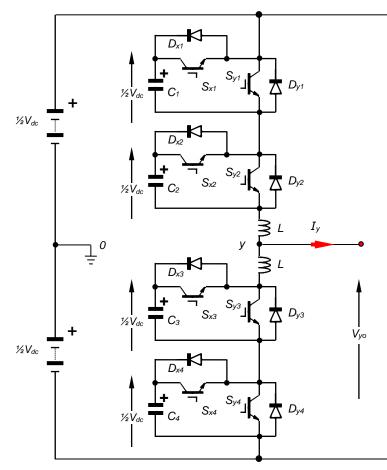

ii. A second multilevel output voltage approach is shown in figure 17.17, where the triangular carriers are not only displaced by 180° in time, but are vertically displaced, as for multilevel inverter pwm generation, which is considered in section 17.4 (half the magnitude and twice the frequency as in figure 17.6). The upper triangle modulates reference values greater than zero, while the lower triangle modulates when the reference is less than zero.

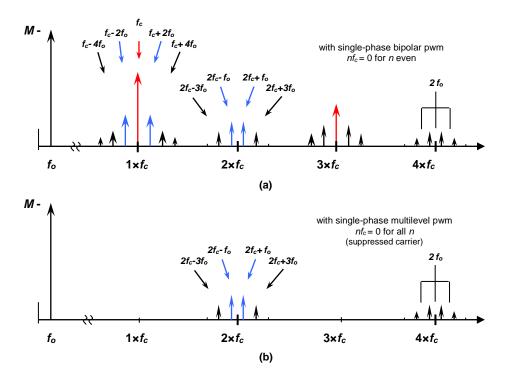

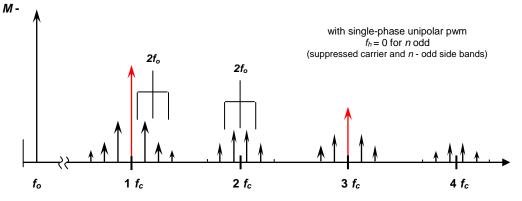

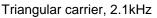

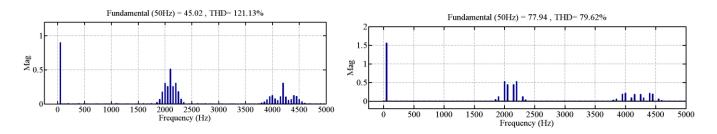

## Spectral comparison between bipolar and multilevel pwm waveforms

The key features of the H-bridge inverter output voltage with bipolar pwm are (fig 17.6a):

- a triangular carrier has only odd Fourier components, so the output spectrum only has carrier components at odd harmonics of the carrier frequency

- the first carrier components occur at the carrier frequency, fc

- side-band components occur spaced by 2f<sub>o</sub> from other components, around all multiples of the carrier frequency f<sub>c</sub>

From figure 17.6b, the key features of the H-bridge inverter output voltage with multilevel pwm are:

- the output switching frequency is double  $2f_c$  each leg switching frequency  $f_c$ , since the switching of each leg is time shifted (by 180°), hence the first carrier related components in the output occur at  $2f_c$  and then at multiples of  $2f_c$  (effectively the carrier is  $2f_o$ )

- no triangular carrier Fourier components exist in the output voltage since the two carriers are in anti-phase (180° apart), effectively cancelling one another in spectrum terms

- side-band components occur spaced by 2fo from other components, around each multiple of the carrier frequency 2fc

Figure 17.6. Typical phase output frequency spectrum, at a give switch commutation frequency, for: (a) bipolar pwm and (b) multilevel pwm.

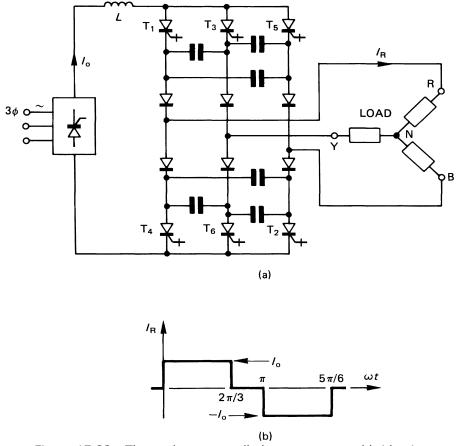

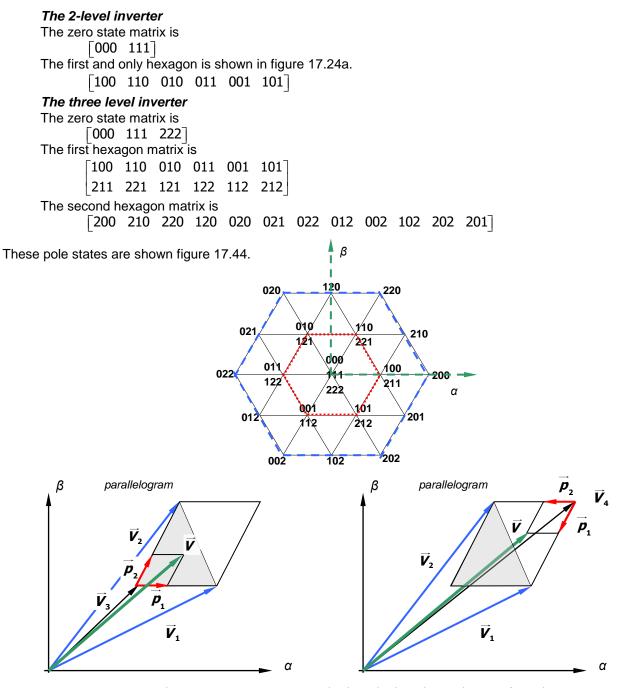

#### 17.1.2 Three-phase voltage-source inverter bridge

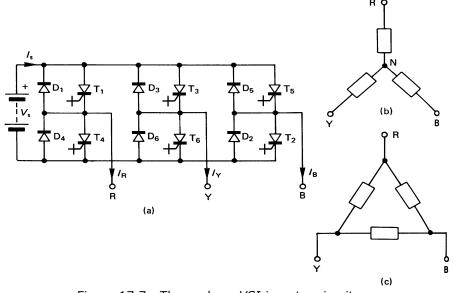

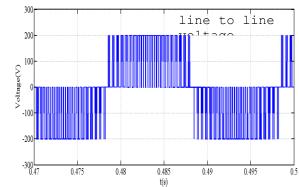

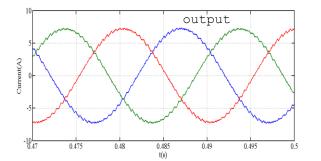

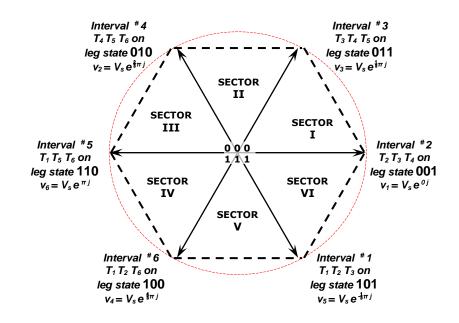

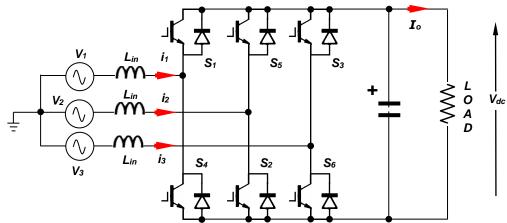

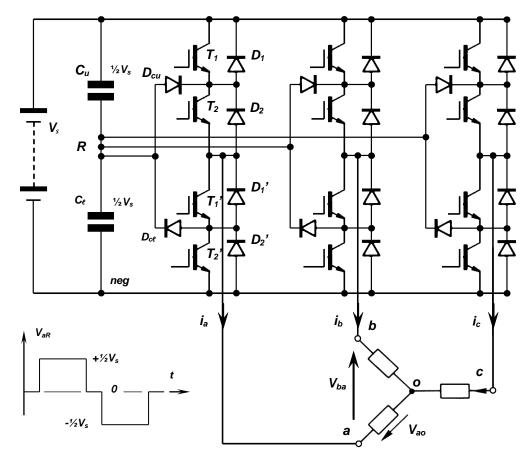

The basic dc to three-phase voltage-source inverter (VSI) bridge is shown in figure 17.7. It comprises six power switches together with six associated reactive energy feedback diodes. Each of the three inverter legs operates at a relative time displacement (phase) of  $\frac{2}{3}\pi$ , 120°.

| Interval | Three conducting switches |                |                |                |                |                |                | leg state      | voltage vector |    |

|----------|---------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|

| 1        | T <sub>1</sub>            | T <sub>2</sub> | T <sub>3</sub> |                |                |                |                |                | 101            | V5 |

| 2        |                           | T <sub>2</sub> | T₃             | T <sub>4</sub> |                |                |                |                | 001            | V1 |

| 3        |                           |                | T <sub>3</sub> | T <sub>4</sub> | T <sub>5</sub> |                |                |                | 011            | V3 |

| 4        |                           |                |                | T <sub>4</sub> | T <sub>5</sub> | $T_6$          |                |                | 010            | V2 |

| 5        |                           |                |                |                | T <sub>5</sub> | $T_6$          | T <sub>1</sub> |                | 110            | V6 |

| 6        |                           |                |                |                |                | T <sub>6</sub> | T <sub>1</sub> | T <sub>2</sub> | 100            | V4 |

Table 17.1:

Quasi-square-wave six conduction states - 180° conduction

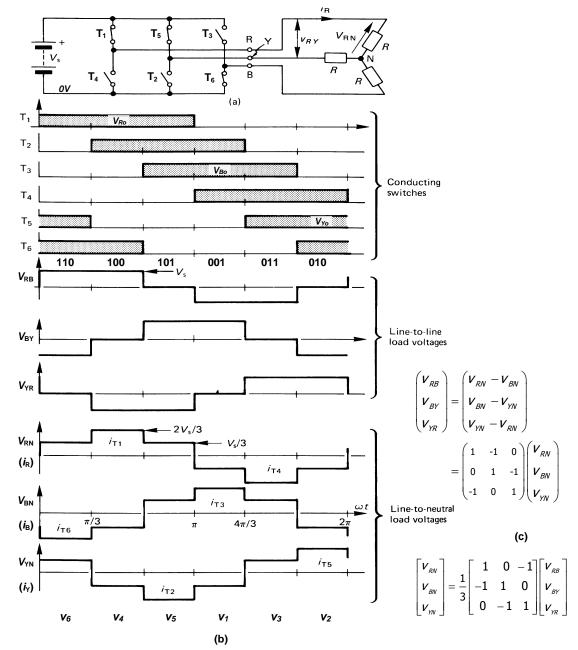

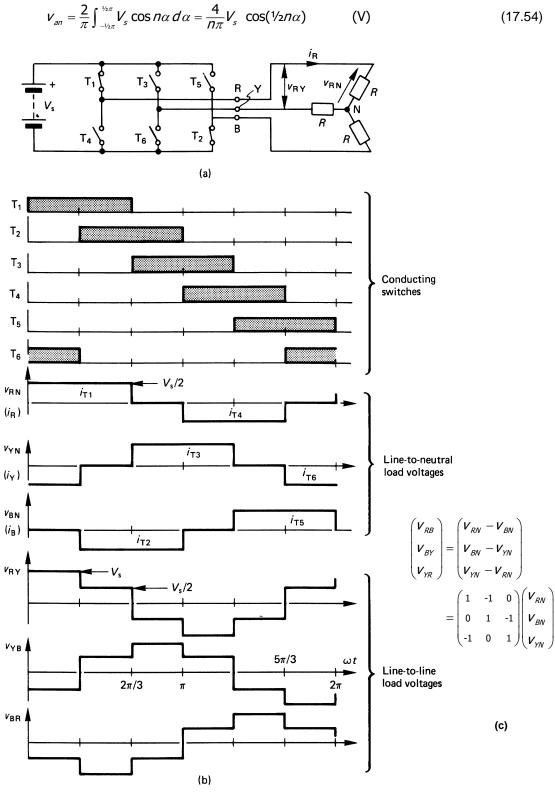

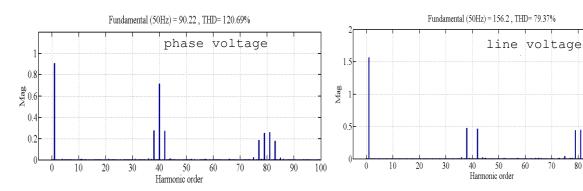

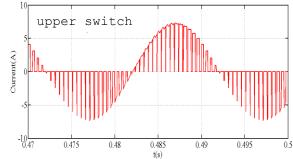

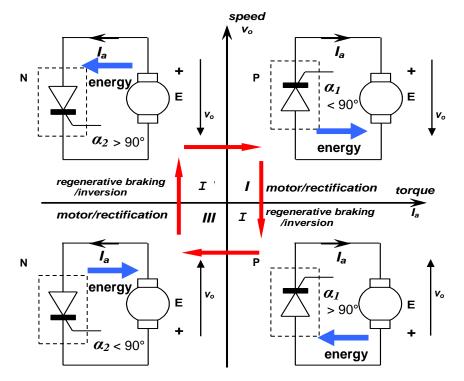

# 17.1.2i - 180° (π) conduction

Figure 17.8 shows inverter bridge quasi-square output voltage waveforms for a 180° switch conduction pattern. Each switch conducts for 180°, such that no two series connected (leg or arm) semiconductor switches across the voltage rail conduct simultaneously. Six patterns exist for one output cycle and the rate of sequencing these patterns,  $6f_o$ , specifies the bridge output frequency,  $f_o$ . The conducting switches during the six distinct intervals are shown and can be summarised as in Table 17.1.

Figure 17.7. Three-phase VSI inverter circuit: (a) GCT thyristor bridge inverter; (b) star-type load; and (c) delta-type load.

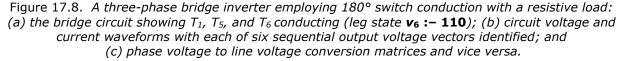

The three output voltage waveforms can be derived by analysing a balanced resistive star load and considering each of the six connection patterns, as shown in figure 17.9, using the matrix in figure 17.8c. Effectively the resistors representing the three-phase load are sequentially cycled anticlockwise one at a time, being alternately connected to each supply rail. The output voltage is independent of the load, as it is for all voltage source inverters.

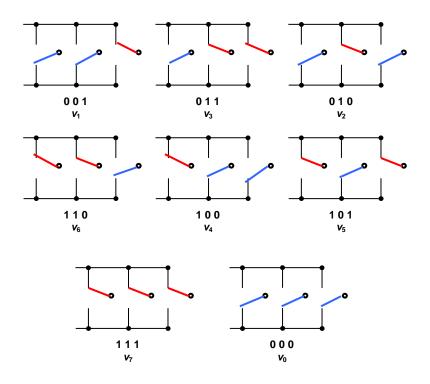

Alternatively, the generation of the three-phase voltages can be analysed analytically by using the rotating voltage space vector technique. With this approach, the output voltage state from each of the three inverter legs (or poles) is encoded as summarised in table 17.1, where a '1' signifies the upper switch in the leg is on, while a '0' means the lower switch is on in that leg. The resultant binary number (one bit for each of the three inverter legs), represents the output voltage vector number (when converted to decimal). The six voltage vectors are shown in figure 17.10 forming sextant boundaries, where the quasi-square output waveform in figure 17.8b is generated by stepping instantaneously from one vector position to another in an anticlockwise direction. Note that the rotational stepping sequence is arranged such that when rotating in either direction, only one leg changes state, that is, one device turns off and then the complementary switch of that led turns on, at each step. This minimises the inverter switching losses. The dwell time of the created rotating vector at each of the six vector positions, is  $\sqrt[1]{3}\pi$  ( $\frac{1}{6}T$ ) of the cycle period (7). Note that the line-to-line zero voltage states 000 and 111 are not used. These represent the condition when *either* all the upper switches  $(T_1, T_3, T_5)$  are on *or* all the lower switches (T<sub>2</sub>, T<sub>4</sub>, T<sub>5</sub>) are switched on (represented as the origin in figure 17.10). Phase reversal can be obtained by interchanging two phase outputs, or as is the preferred method, the direction of the rotating vector sequence is reversed. Reversing is therefore effectively achieved by back-tracking along each output waveform.

With reference to figure 17.8b, the line-to-load neutral voltage Fourier coefficients are given by

$$V_{n_{L-N}} = \frac{2}{3\pi} V_s \frac{2 + \cos\frac{n\pi}{3} - \cos\frac{2n\pi}{3}}{n}$$

(17.45)

The line-to-load neutral voltage is therefore

$$V_{n_{L-N}} = \frac{2}{\pi} V_s \sum_{n=1,6r\pm 1}^{\infty} \frac{\sin n \,\omega t}{n} \qquad r = 1, 2, 3, \dots$$

(17.46)

that is

$$V_{RN} = \frac{2}{\pi} V_{s} \left[ \sin \omega t + \frac{1}{5} \sin 5\omega t + \frac{1}{7} \sin 7\omega t + \frac{1}{11} \sin 11\omega t + \ldots \right]$$

(V) (17.47)

similarly for  $v_{YN}$  and  $v_{BN}$ , where  $\omega t$  is substituted by  $\omega t + \frac{2}{3}\pi$  and  $\omega t - \frac{2}{3}\pi$  respectively.

The line-to-line voltage, from equation (17.38) with  $\alpha = \frac{1}{3}\pi$ , gives Fourier coefficients defined by

$$V_{n_{L-L}} = \frac{4}{\pi} V_s \frac{\left(\cos\frac{n\pi}{6}\right)}{n}$$

(17.48)

The line-to-line voltage is thus

$$V_{n_{L-L}} = \frac{2\sqrt{3}}{\pi} V_s \sum_{n=1,6r\pm 1}^{\infty} \left\| \cos \frac{n\pi}{6} \right\| \frac{\sin n\,\omega t}{n} \qquad r = 1, 2, 3, .$$

(17.49)

(the || || symbol provides the sign), that is

$$V_{RB} = \frac{2\sqrt{3}}{\pi} V_{s} \left[ \sin \omega t - \frac{1}{5} \sin 5\omega t - \frac{1}{7} \sin 7\omega t + \frac{1}{11} \sin 11\omega t + \dots \right]$$

(V) (17.50)

and similarly for  $v_{BY}$  and  $v_{YR}$ . Figure 17.8b shows that  $v_{RB}$  is shifted  $\frac{1}{6}\pi$  with respect to  $v_{RN}$ , hence to obtain the three line voltages while maintaining a  $v_{RN}$  reference,  $\omega t$  should be substituted with  $\omega t + \frac{1}{6}\pi$ ,  $\omega t - \frac{1}{2}\pi$  and  $\omega t + \frac{5}{6}\pi$ , respectively. The three line-to-line fundamental voltages are:

$$V_{AB,1} = \frac{2\sqrt{3}}{\pi} V_s \sin\left(\omega t + \frac{1}{6}\pi\right)$$

$$V_{BC,1} = \frac{2\sqrt{3}}{\pi} V_s \sin\left(\omega t - \frac{1}{2}\pi\right)$$

$$V_{CA,1} = \frac{2\sqrt{3}}{\pi} V_s \sin\left(\omega t + \frac{5}{6}\pi\right)$$

Since the interphase voltages consist of two square waves displaced by  $\frac{2}{3}\pi$ , no triplen harmonics (3, 6, 9, . . .) exist. The outputs comprise harmonics given by the series  $n = 6r \pm 1$  where  $r \ge 0$  and is an integer. The *n*th harmonic has a magnitude of 1/n relative to the fundamental.

Figure 17.9. Determination of the line-to-neutral voltage waveforms for a balanced resistive load and 180° conduction as illustrated in figure 17.8.

By examination of the interphase output voltages in figure 17.8 it can be established that the mean halfcycle voltage is  $\frac{2}{3}V_s$  and the rms value is  $\sqrt{\frac{2}{3}} V_s$ , namely 0.816  $V_s$ . From equation (17.50) the rms value of the fundamental is  $\sqrt{6} V_s/\pi$ , namely 0.78  $V_s$ , that is  $3/\pi$  times the total rms voltage value. The three-phase inverter output voltage properties are summarised in Table 17.2.

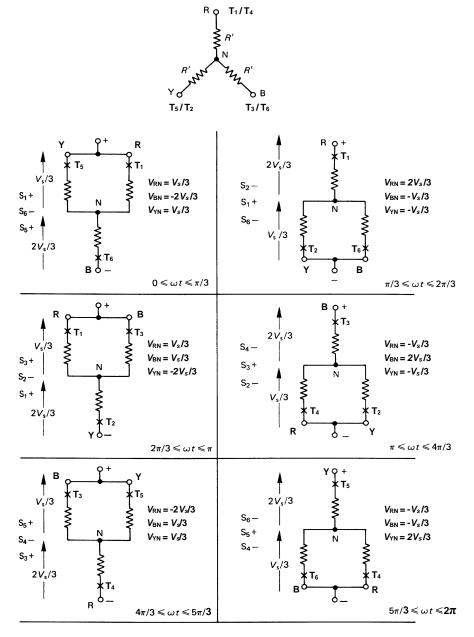

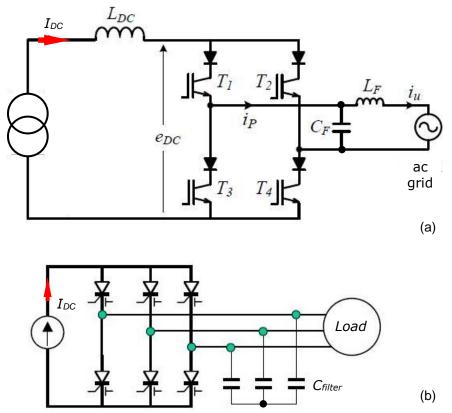

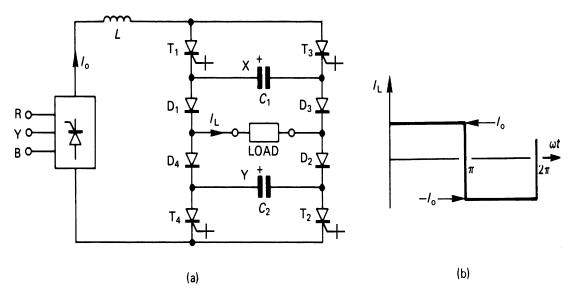

## 17.1.2ii - 120° (<sup>3</sup>/<sub>3</sub>π) conduction

The basic three-phase inverter bridge in figure 17.7 can be controlled with each switch conducting for 120°. As a result, at any instant only two switches (one upper and one non-complementary lower) conduct and the resultant quasi-square output voltage waveforms are shown in figure 17.12. A 60° ( $\frac{1}{3}\pi$ ), dead time exists between two series switches conducting, thereby providing a safety margin against *simultaneous conduction* of the two series devices (for example T<sub>1</sub> and T<sub>4</sub>) across the dc supply rail. This safety margin is obtained at the expense of a lower semi-conductor device utilisation and rms output voltage than with 180° device conduction. The device conduction pattern is summarised in Table 17.3. A feature with  $\frac{2}{3}\pi$  conduction is that the phase currents can be measured from the dc link current.

Figure 17.10. Generation and arrangement of the six quasi-square inverter output voltage states.

Figure 17.8b for 180° conduction and 17.12b for 120° conduction show that the line to neutral voltage of one conduction pattern is proportional to the line-to-line voltage of the other. That is, from equation (17.38) with  $\alpha = \frac{1}{3}\pi$

$$V_{RN}(\frac{2}{3}\pi) = \frac{1}{2}V_{RY}(\pi) = \sum_{n=1,3,5}^{\infty} \frac{2}{\pi n} V_s \cos \frac{n\pi}{6} \sin n\omega t$$

$$= \frac{\sqrt{3}}{\pi} V_s \left[ \sin \omega t - \frac{1}{5} \sin 5\omega t - \frac{1}{7} \sin 7\omega t + \frac{1}{11} \sin 11\omega t + \dots \right]$$

(V)

and

$$\mathcal{V}_{RY}\left(\frac{2}{3}\pi\right) = \frac{3}{2}\mathcal{V}_{RN}\left(\pi\right) = \sum_{n=1,3,5}^{\infty} \frac{2\sqrt{3}}{\pi n} \mathcal{V}_{s} \cos\frac{n\pi}{6} \sin n\omega t

= \frac{3}{\pi} \mathcal{V}_{s}\left[\sin\omega t + \frac{1}{5}\sin5\omega t + \frac{1}{7}\sin7\omega t + \frac{1}{11}\sin11\omega t + \dots\right]$$

(V)

Also  $v_{RY} = \sqrt{3} v_{RN}$  and the phase relationship between these line and phase voltages, of  $\frac{1}{6}\pi$ , has not been retained. That is, with respect to figure 17.12b, substitute  $\omega t$  with  $\omega t + \frac{1}{6}\pi$  in equation (17.51) and  $\omega t + \frac{1}{3}\pi$  in equation (17.52). 180° conduction gives a 15% increase in ac voltage magnitude compared to 120° conduction, but both techniques give the same harmonic spectrum components.

The output voltage properties for both 120° and 180° conduction are summarised in the Table 17.2.

Independent of the conduction angle (120°, 180° or even 150°), quasi-square 180° conduction occurs with inductive loads, producing the six hexagon states shown in the upper part of figure 17.10. The resistive load assumptions made in this section for explanation purposes can be misleading.

| Conduction       | Fundamer                      | ntal voltage               | Characteristic                |                          |                            |  |  |

|------------------|-------------------------------|----------------------------|-------------------------------|--------------------------|----------------------------|--|--|

| period           | peak                          | rms                        | Total rms                     | <b>Distortion Factor</b> | THD                        |  |  |

|                  | $V_{_1}$                      | $V_1$                      | $V_{rms}$                     | μ                        | thd                        |  |  |

| 180°             | (V)                           | (V)                        | (V)                           |                          |                            |  |  |

| Phase<br>Voltage | $\frac{2}{\pi}V_s$            | $\frac{\sqrt{2}}{\pi}V_s$  | $\frac{\sqrt{2}}{3}V_{s}$     | $\frac{3}{\pi}$          | $\sqrt{\frac{\pi^2}{9}-1}$ |  |  |

| VL-N             | $= 0.637 V_s$                 | $= 0.450 V_{s}$            | = 0.471 <i>V</i> <sub>s</sub> | = 0.955                  | = 0.311                    |  |  |

| Line<br>Voltage  | $\frac{2\sqrt{3}}{\pi}V_{s}$  | $\frac{\sqrt{6}}{\pi}V_s$  | $\sqrt{\frac{2}{3}} V_s$      | $\frac{3}{\pi}$          | $\sqrt{\frac{\pi^2}{9}-1}$ |  |  |

| V <i>L- L</i>    | $= 1.10 V_{s}$                | $= 0.78 V_s$               | $= 0.816 V_{s}$               | = 0.955                  | = 0.311                    |  |  |

| 120°             | (V)                           | (V)                        | (V)                           |                          |                            |  |  |

| Phase<br>Voltage | $\frac{\sqrt{3}}{\pi}V_s$     | $\frac{\sqrt{6}}{2\pi}V_s$ | $\frac{1}{\sqrt{6}}V_s$       | $\frac{3}{\pi}$          | $\sqrt{\frac{\pi^2}{9}-1}$ |  |  |

| V <sub>L-N</sub> | $= 0.551 V_s$                 | $= 0.390 V_{s}$            | $= 0.408 V_{s}$               | = 0.955                  | = 0.311                    |  |  |

| Line<br>Voltage  | $\frac{3}{\pi}V_s$            | $\frac{3}{\sqrt{2}\pi}V_s$ | $\frac{1}{\sqrt{2}}V_{s}$     | $\frac{3}{\pi}$          | $\sqrt{\frac{\pi^2}{9}-1}$ |  |  |

| V                | = 0.955 <i>V</i> <sub>s</sub> | $= 0.673 V_s$              | = 0.707 <i>V</i> <sub>s</sub> | = 0.955                  | = 0.311                    |  |  |

Table 17.2: Quasi-squarewave voltage properties for a resistive load

Table 17.3:

Quasi-squarewave conduction states - 120° conduction

| Interval | Two conducting devices |                |                |                |                |                |                |

|----------|------------------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1        | T <sub>1</sub>         | T <sub>2</sub> |                |                |                |                |                |

| 2        |                        | T <sub>2</sub> | T <sub>3</sub> |                |                |                |                |

| 3        |                        |                | T <sub>3</sub> | T <sub>4</sub> |                |                |                |

| 4        |                        |                |                | T <sub>4</sub> | T <sub>5</sub> |                |                |

| 5        |                        |                |                |                | T <sub>5</sub> | T <sub>6</sub> |                |

| 6        |                        |                |                |                |                | T <sub>6</sub> | T <sub>1</sub> |

An ideal switch model of the three-phase voltage source inverter, with 180° conduction, connected to passive load, where  $(T_1, T_4)$ ,  $(T_5, T_2)$  and  $(T_3 \text{ and } T_6)$  represent complementary switch pairs, can be describe by:  $T_1+T_4=1$ ;  $T_5+T_2=1$  and  $T_3+T_6=1$ . The upper and lower switches in the same arm operate in a complementary manner, that is, turning on  $T_1$  corresponds to  $T_1=1$  and  $T_4=0$ , and similarly phases Y and B. Then the inverter terminal voltages at R, Y and B relative to supply mid-point 'o' can be synthesized from dc link voltage as:

$$\begin{aligned} \boldsymbol{v}_{Ro} &= \boldsymbol{\mathcal{V}}_{2}(\mathsf{T}_{1}\text{-}\mathsf{T}_{4})\boldsymbol{\mathcal{V}}_{s} \\ \boldsymbol{v}_{\gamma o} &= \boldsymbol{\mathcal{V}}_{2}(\mathsf{T}_{5}\text{-}\mathsf{T}_{2})\boldsymbol{\mathcal{V}}_{s} \\ \boldsymbol{v}_{Bo} &= \boldsymbol{\mathcal{V}}_{2}(\mathsf{T}_{3}\text{-}\mathsf{T}_{6})\boldsymbol{\mathcal{V}}_{s} \end{aligned}$$

With T<sub>1</sub> on and T4 off, the converter output phase R is connected to  $\frac{1}{2}V_s$ , while T<sub>1</sub> off and T<sub>4</sub> on connects output phase R to  $-\frac{1}{2}V_s$ .

The equations describing the ac side transients for a three-phase load R<sub>R</sub>, R<sub>Y</sub>, R<sub>B</sub>, and L<sub>R</sub>, L<sub>Y</sub>, L<sub>B</sub> are:

$$\frac{d}{dt}\begin{bmatrix}i_{R}\\i_{Y}\\i_{B}\end{bmatrix} = \begin{bmatrix}\frac{V_{Rn}}{L_{R}}\\\frac{V_{Yn}}{L_{Y}}\\\frac{V_{Bn}}{L_{B}}\end{bmatrix} - \begin{bmatrix}\frac{R_{R}}{L_{R}} & 0 & 0\\0 & \frac{R_{Y}}{L_{Y}} & 0\\0 & 0 & \frac{R_{B}}{L_{B}}\end{bmatrix}\begin{bmatrix}i_{R}\\i_{Y}\\i_{B}\end{bmatrix}$$

where  $v_{Rn}$ ,  $v_{Yn}$  and  $v_{Bn}$  are phase voltages relative to the load floating neutral-point 'n', where  $i_R+i_Y+i_B=0$ .

Figure 17.11. Derivation tree for three-phase bridge inverter output frequency and magnitude control techniques.

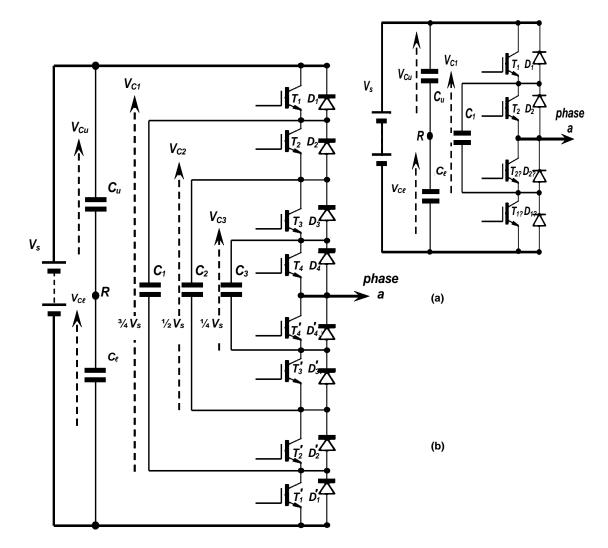

# 17.1.3 Inverter ac output voltage and frequency control techniques

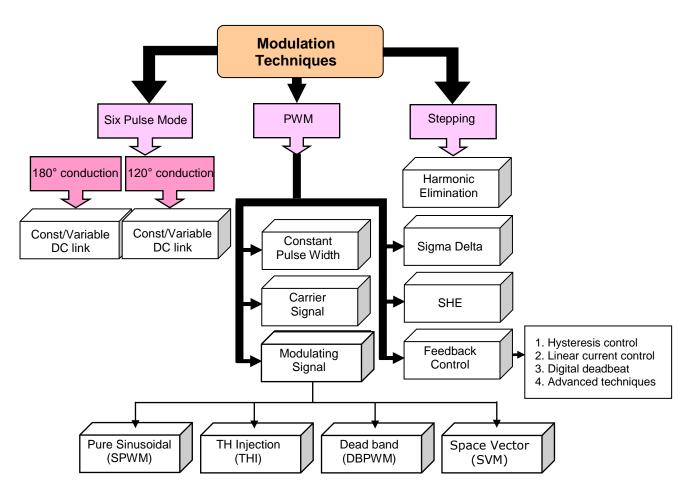

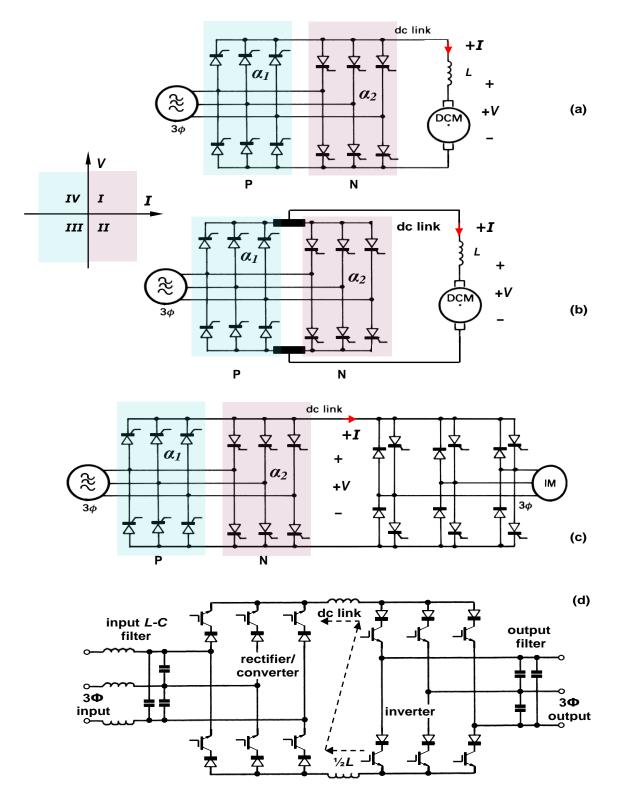

It is a common requirement that the output voltage and/or frequency of an inverter be varied in order to control the load power or, in the case of an induction motor, to control the shaft speed and torque by maintaining a constant V/f ratio. The six VSI modulation control techniques to be considered are:

- Variable voltage dc link

- Single-pulse width modulation

- Multi-pulse width modulation

- Multi-pulse, selected notching modulation

- Sinusoidal pulse width modulation

- Triplen injection

- Triplens injected into the modulation waveform

- Voltage space vector modulation

- Selected harmonic elimination, SHE

Inverter voltage and frequency control techniques are summarised in figure 17.11.

# 17.1.3i - Variable voltage dc link

The rms voltage of a square-wave can be changed and controlled by varying the dc link source voltage. A *variable dc link* voltage can be achieved with a dc chopper as considered in chapter 16 or an ac phase-controlled thyristor bridge as considered in sections 14.2 and 14.4. A dc link *L-C* smoothing filter may be necessary.

# 17.1.3ii - Single-pulse width modulation

Simple pulse-width control can be employed as considered in section 17.1.1b, where a single-phase bridge is used to produce a quasi-square-wave output voltage as shown in figure 17.1c.

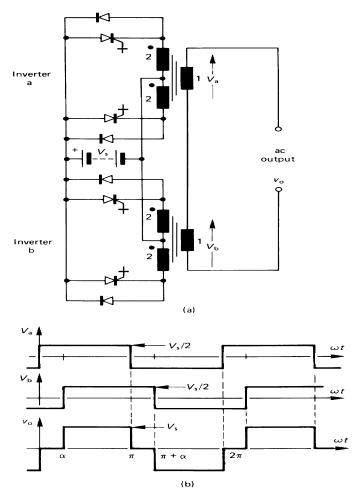

An alternative method of producing a quasi-square wave of controllable pulse width is to transformeradd the square-wave outputs from two push-pull bridge inverters as shown in figure 17.13a. By phaseshifting the output by  $\alpha$ , a quasi-square sum results as shown in figure 17.13b. The output voltage can be described by

$$V_o = \sum_{n \text{ odd}}^{\infty} v_{an} \sin n\omega t \qquad (V)$$

(17.53)

where

Figure 17.12. A three-phase bridge inverter employing 120° switch conduction with a resistive star load: (a) the bridge circuit showing  $T_1$  and  $T_2$  conducting; (b) circuit voltage and current waveforms; and (c) phase voltage to line voltage conversion matrix.

The rms output voltage is

$$V_r = V_s \sqrt{1 - \frac{\alpha}{\pi}}$$

(V) (17.55)

and the rms value of the fundamental is

$$V_1 = \frac{2\sqrt{2}}{\pi} V_s \cos \frac{1}{2\alpha}$$

(V) (17.56)

As  $\alpha$  increases, the magnitude of the harmonics, particularly the third, becomes significant compared with the fundamental magnitude. This type of control may be used in high power applications.

Figure 17.13. Voltage control by combining phase-shifted push-pull inverters: (a) two inverters with two transformers for summing and (b) circuit voltage waveforms for a phase displacement of α.

# Example 17.5: Single-pulse width modulation

Two single-phase H-bridge inverter outputs are transformer added, as shown in figure 17.13. Each inverter operates at 50Hz but phase shifted so as to produce 240V rms fundamental output when the rail voltage of each inverter is 340V dc and the transformers turns ratios are 2:2:1.

Determine

- *i.* the phase shift between the two single phase inverters

- *ii.* the rms output voltage

- *iii.* the frequency and magnitude of the first 4 harmonics of 50Hz and their rms ac contribution to the rms output

- iv. rms voltage of higher order harmonics (higher frequencies than those in part iii.)

- *v.* the total harmonic distortion of the output voltage.

# Solution

*i.* The output is a quasi-square waveform of magnitude  $\pm 340V$  dc. The magnitude of the 50Hz fundamental is given by equation (17.54), for n = 1:

$$V_{a1} = \frac{4}{\pi} V_s \cos(\frac{1}{2}\alpha)$$

$$\sqrt{2} 240V = \frac{4}{\pi} \times 340V \times \cos(\frac{1}{2}\alpha)$$

from which the phase shift is 76.7°, 1.34 radians.

*ii.* The rms output voltage is given by equation (17.55), that is

$$V_{rms} = V_s \sqrt{1 - \alpha_{\pi}} = 340V \sqrt{1 - 1.34_{\pi}} = 257.5V$$

| harmonic<br>n | $V_{an} = \frac{4}{n\pi} V_s \cos(1/2n\alpha)$ | V <sub>an</sub> <sup>2</sup> |

|---------------|------------------------------------------------|------------------------------|

| 3             | -61.4                                          | 3765.0                       |

| 5             | -84.7                                          | 7175.3                       |

| 7             | -1.4                                           | 1.9                          |

| 9             | 46.6                                           | 2168.5                       |

|               | $\sqrt{\sum}V_{an}^2 =$                        | 114.50                       |

iii. The peak values of the first four harmonics are given in the table below.

The rms value of the ac of the first four harmonics is  $114.5/\sqrt{2} = 81.0V$ .

*iv.* The ac component of the harmonics above the 9<sup>th</sup> is given by

$$V_{rms\,n>9} = \sqrt{V_{rms}^2 - V_{rms\,n\le9}^2}$$

$$= \sqrt{257.5V^2 - (240V^2 + 81.0V^2)} = 46.3V$$

*v.* The total harmonic voltage distortion is given by

$$THD_{v} = \frac{\sqrt{V_{rms}^{2} - V_{a1}^{2}}}{V_{a1}} \times 100 = \sqrt{\left(\frac{V_{rms}}{V_{a1}}\right)^{2} - 1} \times 100$$

$$= \sqrt{\left(\frac{257.5V}{240V}\right)^{2} - 1} \times 100 = 38.9\%$$

Figure 17.14. Inverter control giving variable duty cycle of five notches per half cycle: (a) low duty cycle,  $\delta_1$ , hence low fundamental magnitude, (b) higher duty cycle,  $\delta_2$ , for a high fundamental voltage output, and (c) voltage output spectrum.

# 17.1.3iii - Multi-pulse width modulation

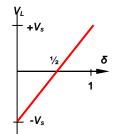

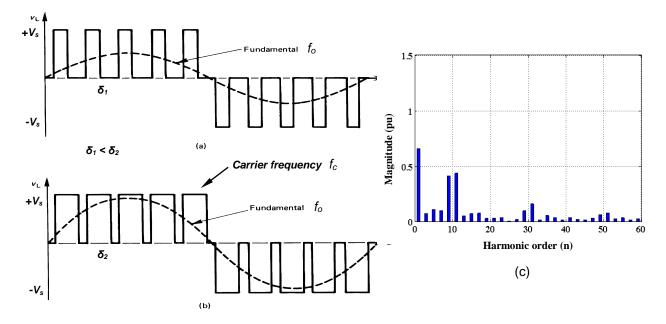

An extension of the single-pulse modulation technique is multiple-notching as shown in figure 17.14. The bridge switches are controlled so as to vary the on to off time of each notch,  $\delta$ , thereby varying the output rms voltage which is given by  $V_{rms} = \sqrt{\delta} V_s$ . Alternatively, the number of notches can be varied.

The harmonic content at lower output voltages is significantly lower than that obtained with single-pulse modulation. The increased switching frequency does increase the magnitude of higher order harmonics and the switching losses. The Fourier coefficients of the output voltage in figure 17.14 are given by

$$V_{n} = \frac{4}{n\pi} \sum_{j=1,2,3,\dots}^{\frac{r}{f_{0}}} \left[ \cos 2\pi \frac{f_{o}}{f_{c}} n \left( 2j - 1 + \delta \right) - \cos 2\pi \frac{f_{o}}{f_{c}} n \left( 2j - 1 - \delta \right) \right]$$

(17.57)

where  $f_o$  is the fundamental frequency,  $f_c$  the triangular carrier frequency and  $0 \le \delta \le 1$  is the duty cycle.

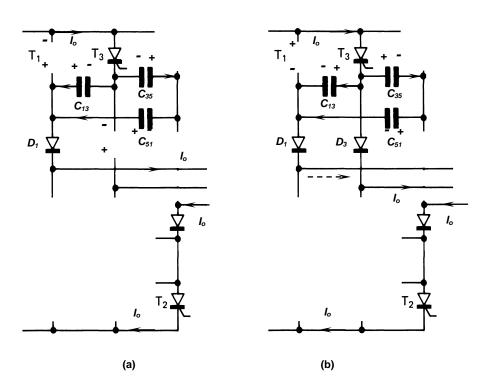

#### 17.1.3iv - Multi-pulse, selected notching modulation - selected harmonic elimination

If a multi-level waveform ( $\pm V_s$ , 0) is used with quarter wave symmetry, as shown in figure 17.15a, then both the harmonics and total rms output voltage can be controlled. With one pulse per quarter wave, the  $k^{th}$  harmonic is eliminated from the output voltage if the centre of the pulse is located such that

$$\sin k\lambda = 0$$

that is  $\lambda = \pi/\mu$

(17.58)

Independent of the pulse width  $\delta$ , the  $k^{th}$  harmonic is eliminated and the other Fourier components are given by

$$V_n = \frac{8}{n\pi} V_s \sin n \frac{\pi}{k} \sin n\delta$$

(17.59)

The output voltage total rms is solely dependent on the pulse width  $\delta$  and is given by

$$V_{orms} = V_s \sqrt{\frac{2}{\pi}} \delta \tag{17.60}$$

On the other hand, the bipolar waveform  $(\pm V_s)$  in figure 17.15b has an rms value of  $V_s$ , independent of the harmonics eliminated.

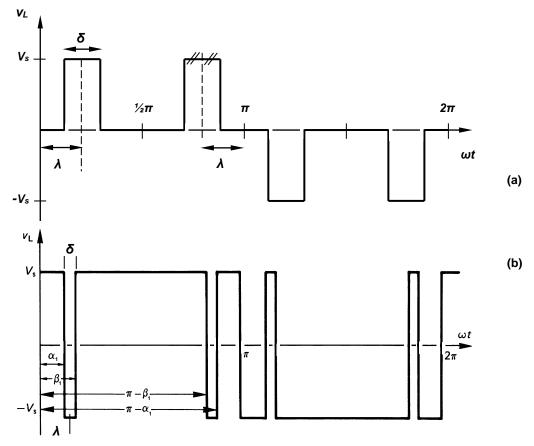

Figure 17.15. Output voltage harmonic reduction for a single-phase bridge using selected notching: (a) multilevel output voltage and (b) bipolar output voltage.

Selected elimination of lower-order harmonics can be achieved by producing an output voltage waveform as shown in figure 17.15b. The exact switching points are calculated off-line so as to eliminate the required harmonics. For n switchings per half cycle, n selected harmonics can be eliminated.

In figure 17.15b two notches per half cycle are introduced; hence any two selected harmonics can be eliminated. The more notches, the lower is the output fundamental. For example, with two notches, the third and fifth harmonics are eliminated. From

$$b_{n} = \frac{4}{\pi} \int_{0}^{V_{2\pi}} f(\theta) \sin n\theta \, d\theta \quad \text{for} \quad n = 1, 2, 3, \dots$$

(17.61)

$$b_{3} = \frac{4}{3\pi} V_{s} \left( 1 - 2\cos 3\alpha + 2\cos 3\beta \right) = 0$$

and

$$b_{5} = \frac{4}{5\pi} V_{s} \left( 1 - 2\cos 5\alpha + 2\cos 5\beta \right) = 0$$

Solving yields  $\alpha_1 = 23.6^{\circ}$  and  $\beta_1 = 33.3^{\circ}$ . The total rms output voltage is  $V_s$ , independent of the harmonics eliminated. The magnitude (whence rms) of each harmonic component is

$$V_n = \frac{4}{n\pi} V_s \left( 1 - 4 \times \sin n\lambda \times \sin n\delta \right)$$

(17.62)

The maximum fundamental rms component of the output voltage waveform is 0.84 of a square wave, which is  $(2\sqrt{2}/\pi)V_s$  when  $\delta = \frac{1}{2}\pi$  which produces a square wave.

Ten switching intervals exist compared with two per cycle for a square-wave, hence switching losses and control circuit complexity are increased.

In the case of a three-phase inverter bridge, the third harmonic does not exist, hence the fifth and seventh ( $b_5$  and  $b_7$ ) can be eliminated with  $\alpha_1 = 16.3^{\circ}$  and  $\beta_1 = 22.1$ . The 5th, 7th, 11<sup>th</sup>, and 13th can be eliminated with the angles 10.55°, 16.09°, 30.91°, and 32.87° respectively. Because the waveforms have quarter wave symmetry, only angles for 90° need be stored.

The output rms voltage magnitude can be varied by controlling the dc link voltage or by transformeradding two phase-displaced bridge outputs as demonstrated in figure 17.13. The output voltage Fourier components in equation (17.62) are modified by equation(17.54) given

$$V_n = \frac{4}{n\pi} V_s \left( 1 - 4 \times \sin n\lambda \times \sin n\delta \right) \cos \frac{1}{2}n\alpha$$

(17.63)

And the total rms output voltage is reduced from  $V_s$ , as given by equation (17.55), that is

$$V_{orms} = V_{s} \sqrt{1 - \alpha / \pi}$$

(V) (17.64)

Thus the fundamental rms magnitude can be changed by introducing an extra constraint to be satisfied, along with the harmonic eliminating constraints (as a result of the extra constraint, one fewer harmonic can now be eliminated for a given number of switchings per quarter cycle).

The multi-pulse selected notching modulation technique can be extended to the *optimal pulse-width modulation method,* where harmonics may not be eliminated, but minimised according to a specific criterion. In this method, the quarter wave output is considered to have a number of switching angles. These angles are selected so as, for example, to eliminate certain harmonics, minimise the rms of the ripple current, or any other desired performance index. The resultant non-linear equations are solved using numerical methods off-line. The computed angles are then stored in a ROM look-up table for use. A set of angles must be computed and stored for each desired level of the voltage fundamental and output frequency.

The optimal pwm approach is particularly useful for high-power, high-voltage GCT thyristor inverters, which tend to be limited in switching frequency by device switching losses.

Generally sinwt+ksin3wt is generated (since the third harmonic of the square wave is not eliminated)

$$b_n = \frac{4}{\pi} \int_0^{\frac{2\pi}{3}} f(\theta) \sin n\theta \ d\theta = \frac{4}{\pi} \int_0^{\frac{2\pi}{3}} 1 \times \sin n\theta \ d\theta$$

For a fundamental magnitude of  $\sqrt{3}$ m of the pu link voltage and to eliminate *N*-1 (*N*-1>2) harmonics:

$$-\sum_{k=1}^{N} (-1)^{k} \cos \alpha_{k} = \frac{1}{4} \left( 2 + (-1)^{N-1} m\pi \right)$$

$$-\sum_{k=1}^{N} (-1)^{k} \cos n\alpha_{k} = \frac{1}{2} \qquad \text{for } n = 5, 7, ..., 3N - \frac{3}{2} - \frac{1}{2} (-1)^{N-1}$$

$$(17.65)$$

where  $\alpha_1 < \alpha_2 < ... < \alpha_N < \frac{1}{2}\pi \left(1 - \frac{1}{6}\left(1 - (-1)^{N-1}\right)\right)$

For *N*-1 even, all  $\alpha_k$  angles are less than  $\frac{1}{2}\pi$  other wise  $\frac{1}{3}\pi$  (when *N*-1 is odd).

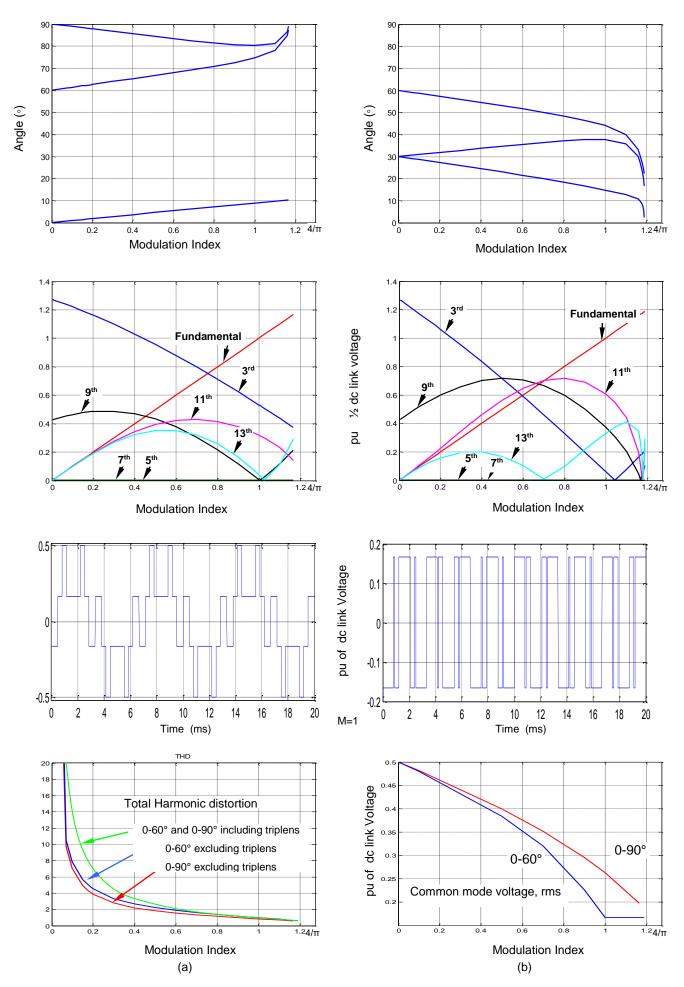

Figure 17.16. SHE commutation angles, normalised as a function of the fundamental eliminating: the 5th and 7<sup>th</sup> harmonics with commutation angles (a) 0 to 90° and (b) 0 to 60°.

To eliminate the 5<sup>th</sup> and 7<sup>th</sup> harmonics (an even number of harmonics), with a fundamental magnitude with modulation index *m*, three angles are required, N=3 and the three equations to be solved are

$$\cos \alpha_1 - \cos \alpha_2 + \cos \alpha_3 = \frac{1}{4} (2 + m\pi)$$

$$\cos 5\alpha_1 - \cos 5\alpha_2 + \cos 5\alpha_3 = \frac{1}{2}$$

$$\cos 7\alpha_1 - \cos 7\alpha_2 + \cos 7\alpha_3 = \frac{1}{2}$$

The resultant angles are shown in figure 17.16. The maximum modulation index, with respect to a square wave is 1.166 and 1.188 for angles less that 60 degrees and greater, respectively. Any solution with all angles less than 60° represents dead banding of the three phases, where each phase is alternately clamped to the dc link zero and positive rails (see section 17.1.3vi). The total harmonic distortion is virtually the same in both cases, as is the maximum common mode voltage dv/dt, while the rms common mode voltage is greater for the case when the angles can exceed 60 degrees.

To eliminate the 5<sup>th</sup>, 7<sup>th</sup>, and 11<sup>th</sup> harmonics (an odd number of harmonics), with a fundamental magnitude with modulation index m, four angles are required, N=4 and the four equations to be solved are

$$\cos \alpha_1 - \cos \alpha_2 + \cos \alpha_3 - \cos \alpha_4 = \frac{1}{4} (2 - m\pi)$$

$$\cos 5\alpha_1 - \cos 5\alpha_2 + \cos 5\alpha_3 - \cos 5\alpha_4 = \frac{1}{2}$$

$$\cos 7\alpha_1 - \cos 7\alpha_2 + \cos 7\alpha_3 - \cos 7\alpha_4 = \frac{1}{2}$$

$$\cos 11\alpha_1 - \cos 11\alpha_2 + \cos 11\alpha_2 - \cos 11\alpha_4 = \frac{1}{2}$$

As further harmonics are eliminated, multiple solutions arise, with at least one solution giving a maximum magnitude tending to 1.155 ( $\pi$ /3) in magnitude, compared to 1.27 (4/ $\pi$ ) for a square wave.

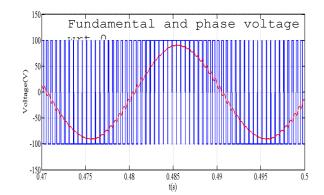

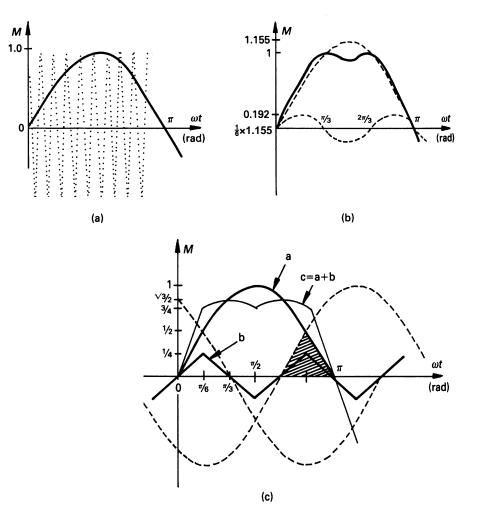

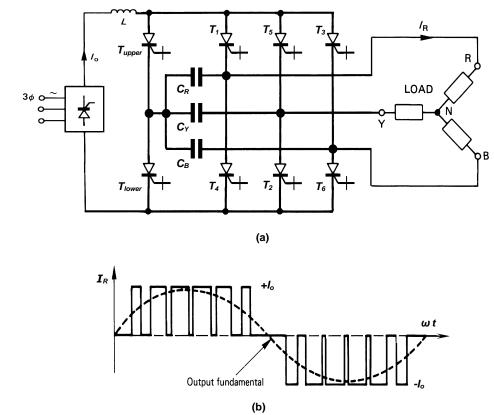

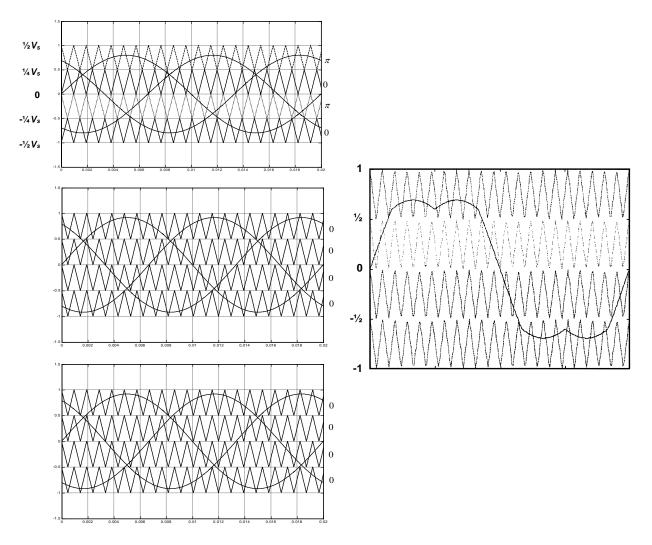

#### 17.1.3v - Sinusoidal pulse-width modulation (pwm), SPWM

#### 1 - Natural sampling

#### (a) Synchronous carrier

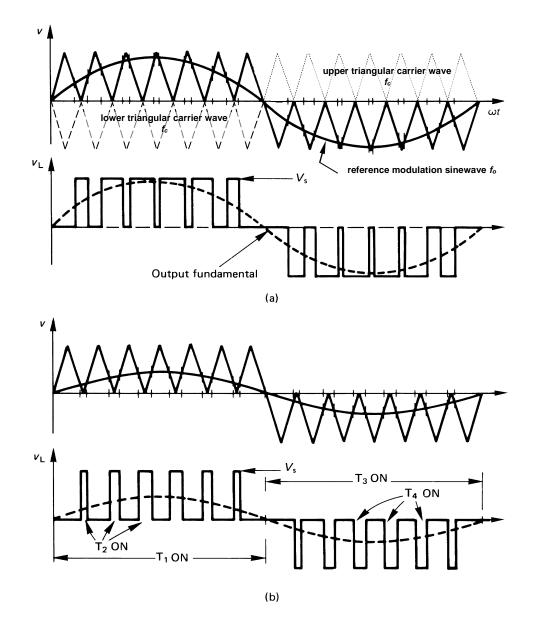

The output voltage waveform and method of generation for synchronous carrier, natural sampling sinusoidal pwm, suitable for the single-phase bridge of figure 17.1, are illustrated in figure 17.17. The switching points are determined by the intersection of the triangular carrier wave  $f_c$  and the reference modulation sine wave,  $f_o$ . The output frequency is at the sine-wave frequency  $f_o$  and the output voltage is proportional to the magnitude of the sine wave. The amplitude M ( $0 \le M \le 1$ ) is called the modulation index. For example, figure 17.17a shows maximum voltage output (M = 1), while in figure 17.17b where the sine-wave magnitude is halved (M = 0.5), the output voltage is halved.

If the frequency of the modulation sinewave,  $f_o$ , is an integer multiple of the triangular wave carrierfrequency,  $f_c$  that is,  $f_c = nf_o$  where *n* is integer, then the modulation is *synchronous*, as shown in figure 17.17. If *n* is odd then the positive and negative output half cycles are symmetrical and the output voltage contains no even harmonics. In a three-phase system if *n* is a multiple of 3 (and odd), the carrier is a triplen of the modulating frequency and the spectrum does not contain the carrier or its harmonics.

$$f_c = (6q + 3) f_o = nf_o$$

(17.66)

for q = 1, 2, 3.

The Fourier harmonic magnitudes of the line to line voltages are given by

$$a_{n} = V_{\ell} \cos\left(\frac{n\pi}{2}\right) \cos\left(\frac{n\pi}{3}\right)$$

$$b_{n} = V_{\ell} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{3}\right)$$

(17.67)

where  $V_{\ell}$  is proportional to the dc supply voltage  $V_s$  and the modulation index *M*.

Sinusoidal pwm requires a carrier of much higher frequency than the modulation frequency. The generated rectilinear output voltage pulses are modulated such that their duration is proportional to the instantaneous value of the sinusoidal waveform at the centre of the pulse; that is, the pulse area is proportional to the corresponding value of the modulating sine wave.

If the carrier frequency is very high, an averaging effect occurs, resulting in a sinusoidal fundamental output with high-frequency harmonics, but minimal low-frequency harmonics.

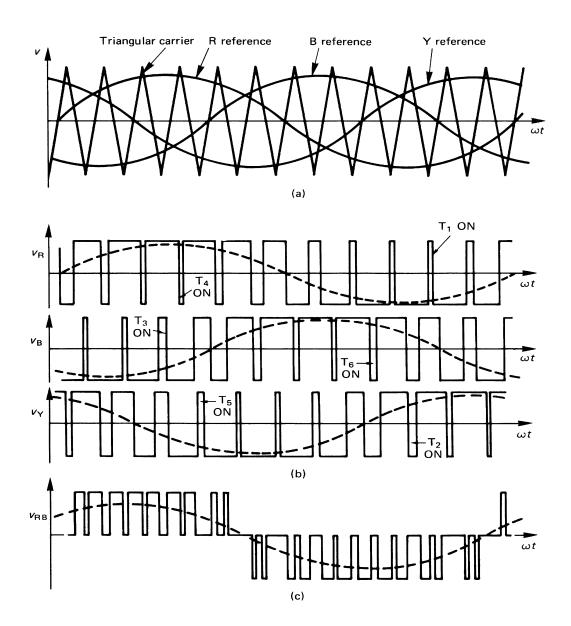

Rather than using two offset triangular carriers, as shown in figure 17.17, a triangular carrier without an offset can be used. Now the output only approximates the ideal. Figure 17.18 shows this pwm generation technique and voltage bipolar output waveform, when applied to the three-phase VSI inverter in figure 17.7. Two offset carriers are not applicable to six-switch, three-phase pwm generation since complementary switch action is required. That is, one switch in the inverter leg must always be on.

Figure 17.17. Derivation of trigger signals for multi-level naturally sampled pulse-width modulation waveforms: (a) for a high fundamental output voltage (M = 1) and (b) for a lower output voltage (M = 0.5), with conducting devices shown.

It will be noticed that, unlike the output in figure 17.17, no zero voltage output periods exist. This has the effect that, in the case of GCT thyristor bridges, a large number of commutation cycles is required. When zero output periods exist, as in figure 17.12, one GCT thyristor is commutated and the complementary device in that leg is not turned on. The previously commutated device can be turned back on without the need to commutate the complementary device, as would be required with the pwm technique illustrated in figure 17.18. Commutation losses are reduced, control circuitry simplified and the likelihood of simultaneous conduction of two series leg devices is reduced.

The alternating zero voltage loop concept can be used, where in figure 17.18b, rather than  $T_1$  being on continuously during the first half of the output cycle,  $T_2$  is turned off leaving  $T_1$  on, then when either  $T_1$  or  $T_2$  must be turned off,  $T_1$  is turned off leaving  $T_2$  on.

Figure 17.18. Naturally sampled pulse-width modulation waveforms suitable for a three-phase bridge inverter: (a) reference signals; (b) conducting devices and fundamental sine waves; and (c) one output line-to-line voltage waveform.

#### (b) Asynchronous carrier

When the carrier is not an integer multiple of the modulation waveform, asynchronous modulation results. Because the output frequency,  $f_o$ , is usually variable over a wide range, it is difficult to ensure  $f_c = nf_o$ . To achieve synchronism, the carrier frequency must vary with frequency  $f_o$ . Simpler generating systems result if a fixed carrier frequency is used, resulting in asynchronism between  $f_o$  and  $f_c$  at most output frequencies. Left over, incomplete carrier cycles create slowly varying output voltages, called subharmonics, which may be troublesome with low carrier frequencies, as found in high-power drives. Natural sampling, asynchronous sinusoidal pwm is usually restricted to analogue or ASIC implementation. The harmonic consequences of asynchronous-carrier natural-sampling are similar to asynchronous-carrier regular-sampling in 2 to follow.

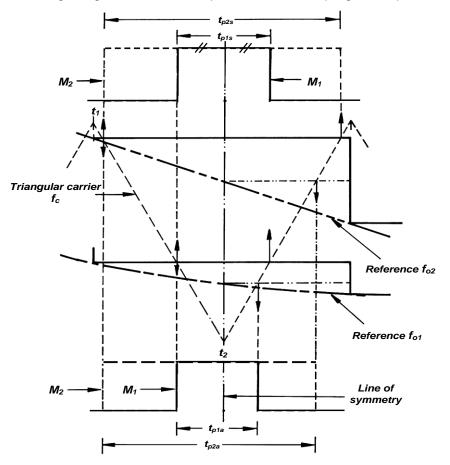

#### 2 - Regular sampling

# (a) Asynchronous carrier

When a fixed carrier frequency is used, usually no attempt is made to synchronise the modulation frequency. The output waveforms do not have quarter-wave symmetry which produces subharmonics. These subharmonics are insignificant if  $f_c >> f_o$ , usually,  $f_c > 20 f_o$ .

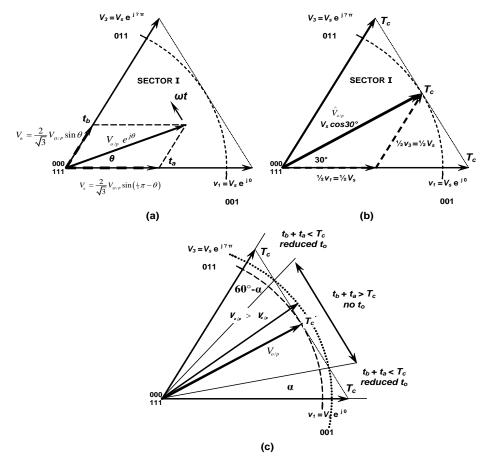

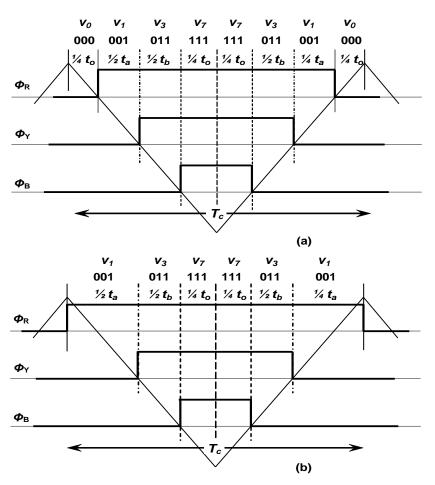

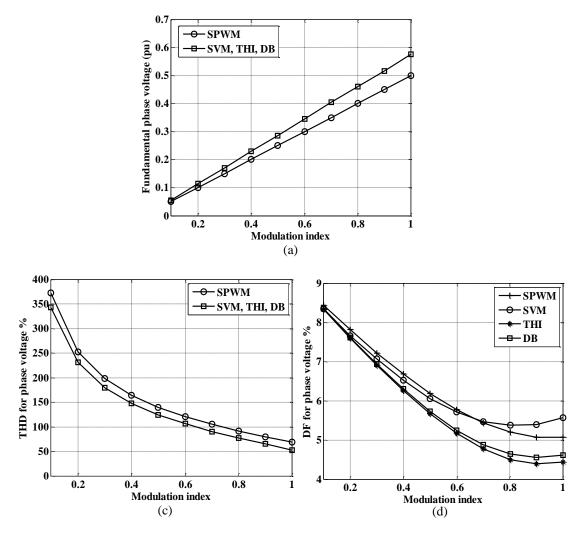

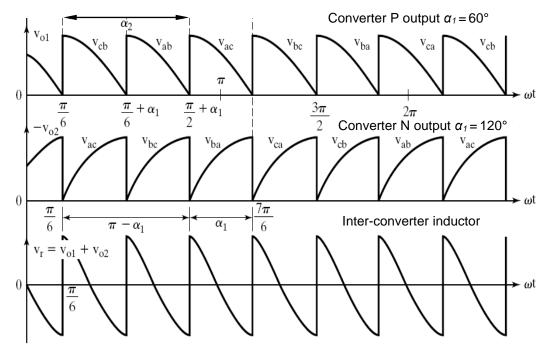

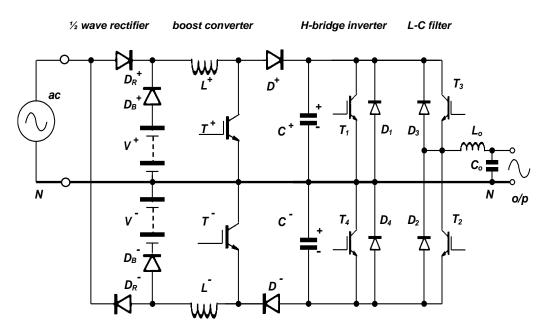

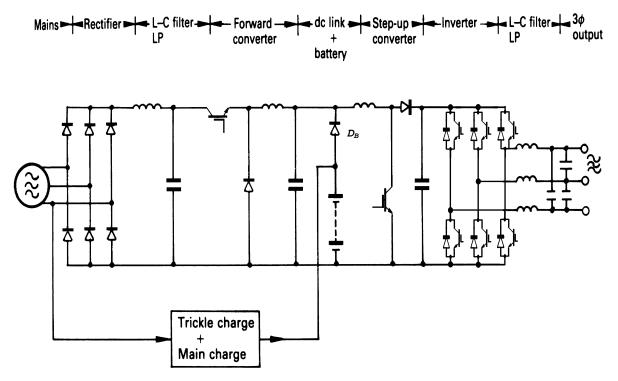

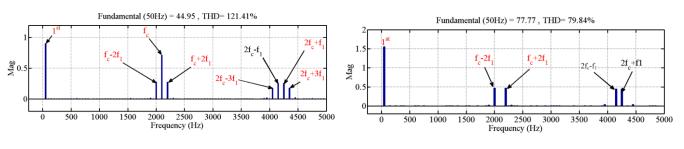

The implementation of sinusoidal pwm with microprocessors or digital signal processors is common because of flexibility and the elimination of analogue circuitry associated problems. The digital pwm generation process involves scaling, by multiplication, of the per unit sine-wave samples stored in ROM.